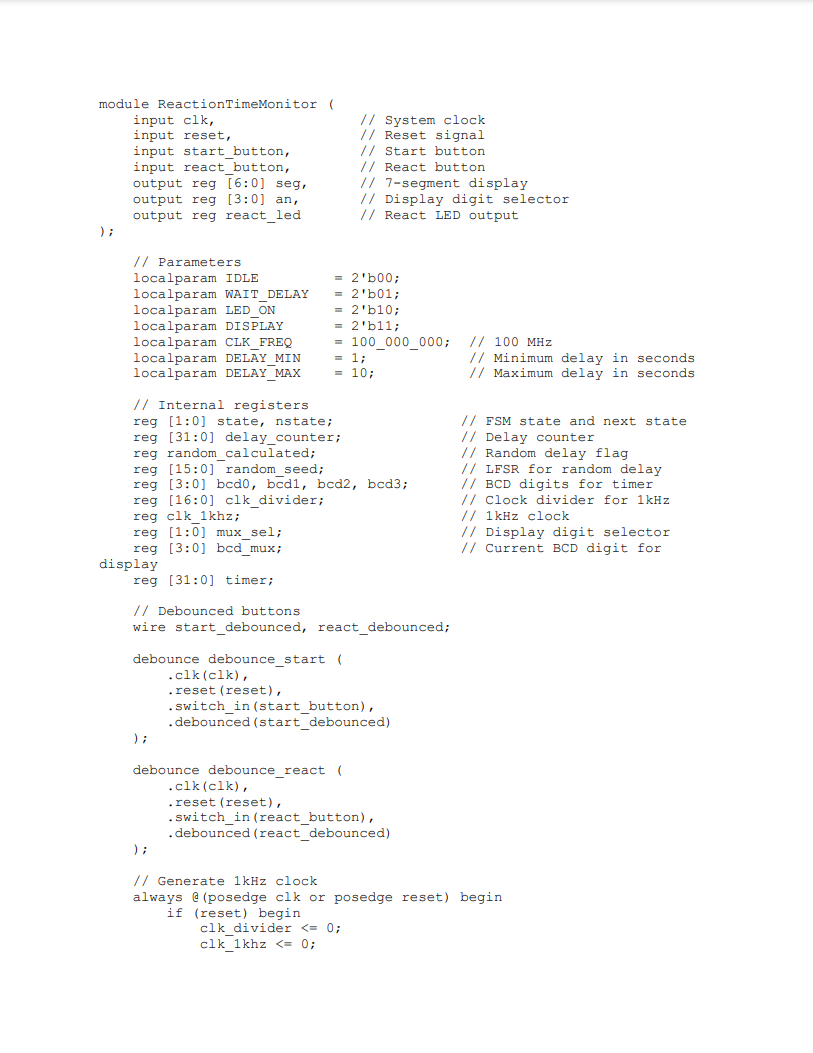

Question: I ' m trying to complete this prompt: Create a Reaction Time Monitor ( RTM ) that can indicate how quickly an user can respond

Im trying to complete this prompt: "Create a Reaction Time Monitor RTM that can indicate how quickly an user can respond to a stimulus. In operation, the RTM is initialized when a start button is pressed. Immediately after the start button is pressed, the seg display is set to show all s and then a random time later between about and seconds a react now LED illuminates and a millisecond timer starts. When the timer starts, the seg display shows the timer value as it counts up in milliseconds.

As quickly as possible after the react LED illuminates, the user must press a react button to stop the timer. The stopped timer will contain the number of milliseconds between the react LED being illuminated and the button being pressed, and that time will be shown on the seg display. Pressing the start button again will clear the timer and begin a new round."

For some reason the react led only has a delay every other time I press the start button and I cant figure out why

module ReactionTimeMonitor

input clk System clock

input reset, Reset signal

input startbutton, Start button

input reactbutton, React button

output reg : seg, segment display

output reg : an Display digit selector

output reg reactled React LED output

;

Parameters

localparam IDLE b;

localparam WAITDELAY b;

localparam LEDON b;

localparam DISPLAY b;

localparam CLKFREQ ; MHz

localparam DELAYMIN ; Minimum delay in seconds

localparam DELAYMAX ; Maximum delay in seconds

Internal registers

reg : state, nstate; FSM state and next state

reg : delaycounter; Delay counter

reg randomcalculated; Random delay flag

reg : randomseed; LFSR for random delay

reg : clkdivider; Clock divider for kHz

reg clkkhz; kHz clock

reg :overline muxsel; Display digit selector

reg : bcdmux; Current BCD digit for

display

reg : timer;

Debounced buttons

wire startdebounced, reactdebounced;

debounce debouncestart

clkclk

resetreset

switchinstartbutton

debouncedstartdebounced

;

debounce debouncereact

clkclk

resetreset

switchinreactbutton

debouncedreactdebounced

;

Generate kHz clock

always @posedge clk or posedge reset begin

if reset begin

clkdivider ;

clkkhz ;

end else if clkdivider d begin

clkdivider ;

clkkhz ~clkkhz;

end else begin

clkdivider clkdivider ;

end

end

Pseudorandom number generator LFSR

Random delay setup to seconds

always @posedge clk or posedge reset begin

if reset begin

delaycounter d;

randomcalculated b;

end else if state WAITDELAY && randomcalculated begin

delaycounter randomseed:DELAYMAX DELAYMIN

DELAYMIN CLKFREQ;

randomcalculated b; Set once random delay is calculated

end else ioverlinefstate WAITDELAY && delaycounter begin

delaycounter delaycounter ;

end else if state IDLE begin

randomcalculated b; Reset flag in IDLE

end

end

Pseudorandom number generator LFSR

always @posedge clk or posedge reset begin

if reset begin

randomseed 'hACE; Arbitrary nonzero seed

end else if state IDLE begin

randomseed randomseed timer:; Add variability with

timer

end else begin

randomseed randomseed: randomseed

randomseed;

end

end

FSM Logic

always @posedge clk or posedge reset begin

if reset begin

state IDLE;

end else begin

state nstate;

end

end

always @ begin

case state

IDLE: begin

if startdebounced begin

nstatoverlinee WAITDELAY;

end else begin

nstate IDLE;

end

end

WAITDELAY: begin

if delaycounter begin

nstate LEDON;

end else begin

nstate WAITDELAY;

end

end

LEDON: begin

if reactdebounced begin

nstate DISPLAY;

end else begin

nstate LEDON;

end

end

DISPLAY: begin

if startdebounced begin

nstate IDLE;

end else begin

nstate DISPLAY;

end

end

default: nstate IDLE;

endcase

end

Timer Logic

always @posedge clkkhz or posedge reset begin

if reset begin

bcdb;

bcdb;

bcdb;

bcdb;

end else if state LEDON begin

if bcdb begin

bcdb;

if bcdb begin

bcdb;

if bcdb begin

bcdb;

if bcdb begin

bcdb; Overflow, reset

end else begin

bcd bcd;

end

end else begin

bcd bcd;

end

end else begin

bcd bcd;

bcd bcd;

end

end

end

React LED logic

always @posedge clk or posedge reset begin

if reset begin

reactled b;

end else if state LEDON && reactdebounced begin

reactled b;

end else begin

reactled b;

end

end

Display MuX

always @posedge clkkhz or posedge reset begin

if reset begin

muxsel b;

end else begin

muxsel muxsel ;

end

end

always @ begin

case muxsel

b:

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock