Question: I mainly need help with this question, although, any additional information is appreciated such as code or pointing me in the right direction! Thanks! 1a)

I mainly need help with this question, although, any additional information is appreciated such as code or pointing me in the right direction! Thanks!

1a) You have to write an abstract at the beginning of the project report to describe what you are doing in the project.

b) You should include an introduction for the project explaining with diagrams the connection you expect between all the stages and what would be the benefit of using that architecture in the computer organization field.

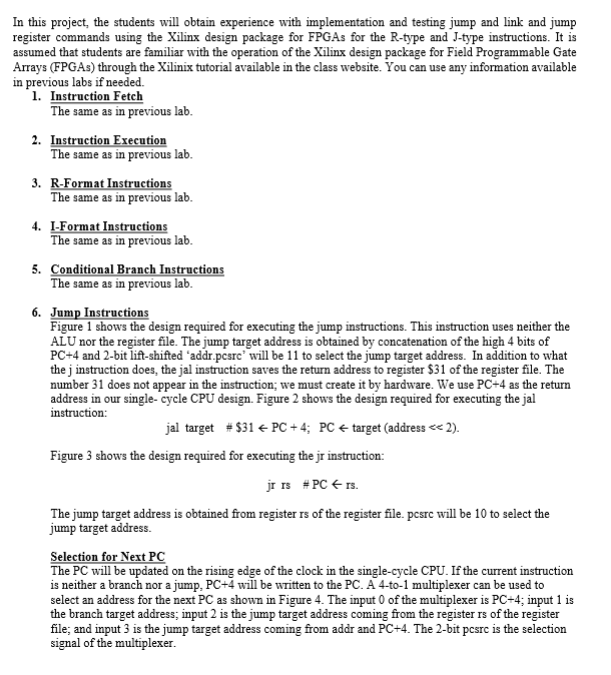

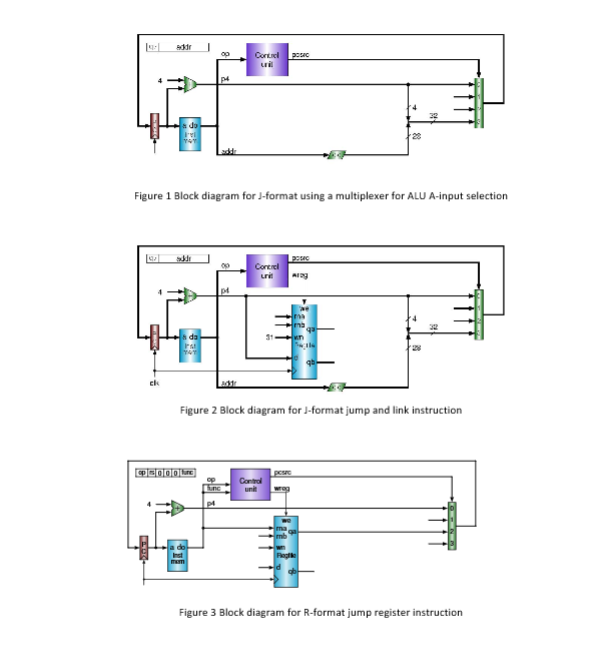

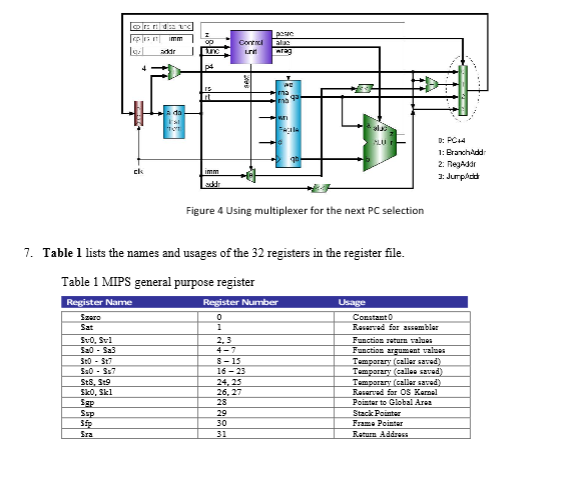

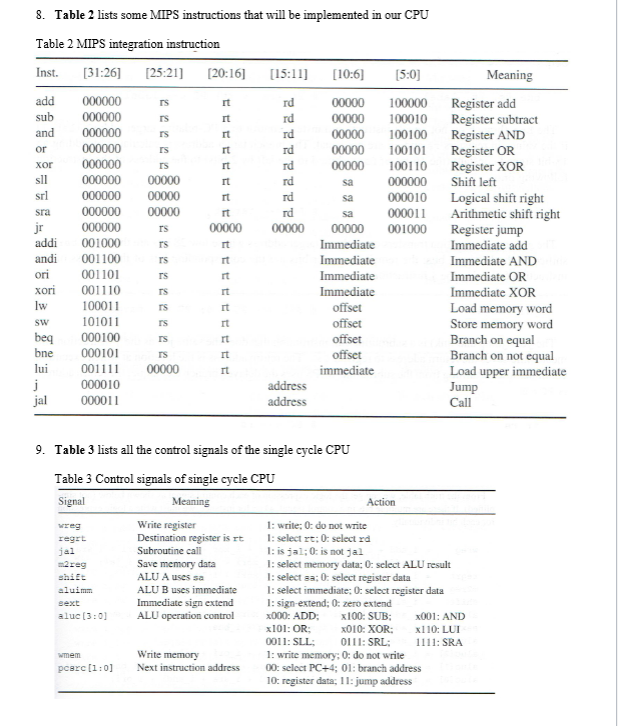

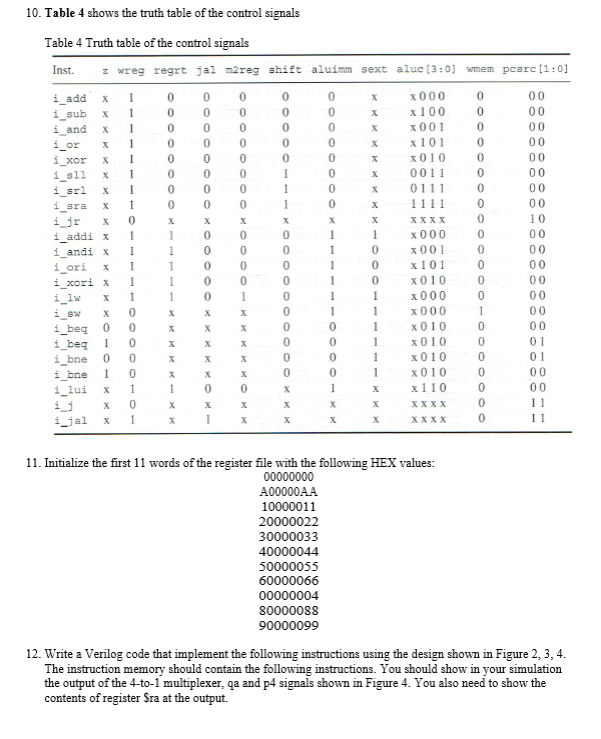

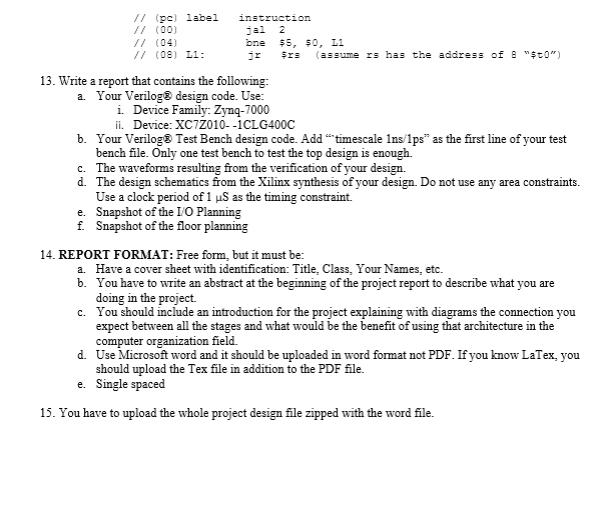

In this project, the students will obtain experience with implementation and testing jump and link and jump register commands using the Xilinx design package for FPGAs for the R-type and J-type instructions. It is assumed that students are familiar with the operation of the Xilinx design package for Field Programmable Gate Arrays (FPGAs) through the Xilinix tutorial available in the class website. You can use any information available in previous labs if needed. 1. Instruction Fetch The same as in previous la b. 2. Instruction Execution The same as in previous lab The same as in previous lab 4. ons The same as in previous lab 5. Conditional Branch Instructions The same as in previous lab. 6. Jump Instructions Figure 1 shows the design required for executing the jump instructions. This instruction uses neither the ALU nor the register file. The jump target address is obtained by concatenation of the high 4 bits of PC+4 and 2-bit lift-shifted addr.pcsrc will be 11 to select the jump target address. In addition to what the j instruction does, the jal instruction saves the return address to register S31 of the register file. The number 31 does not appear in the instruction; we must create it by hardware. We use PC+4 as the return address in our single- cycle CPU design. Figure 2 shows the design required for executing the jal nstruction: Jal target # $31 PC+ 4; PC target (address

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts