Question: I need a Verilog code with a test bench for the FSM and the ALU plus the top modules as well. For the second milestone,

I need a Verilog code with a test bench for the FSM and the ALU plus the top modules as well. For the second milestone, you are required to check o

projectspecific items with your lab TA by

its deadline. You are required to complete the tasks below. Make sure you also refer to each project

for its specific required items.

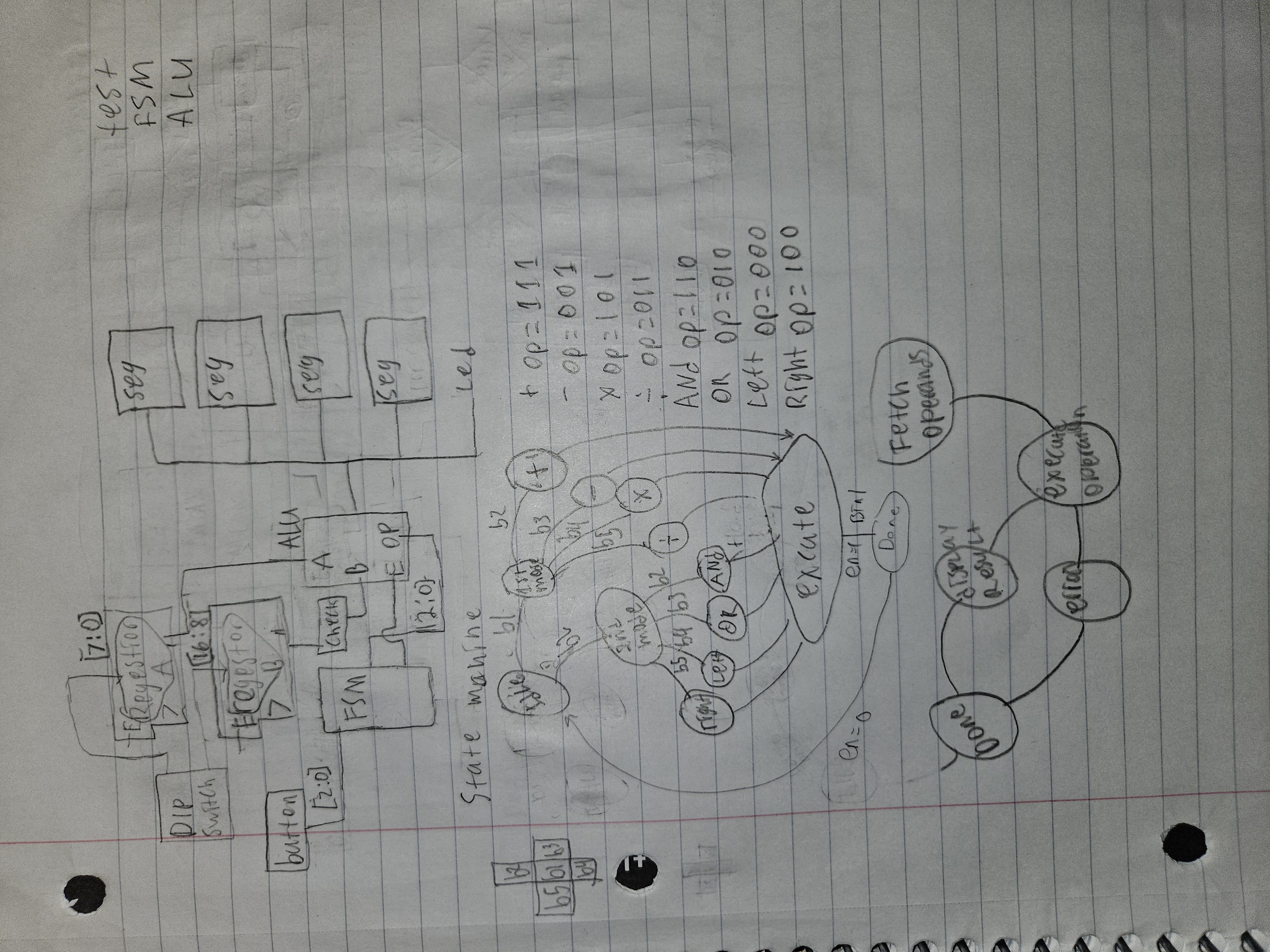

Revised highlevel FSM or ASM chart, datapath design, and controller FSM

Verilog implementation of all modules of your design with verified syntax check from Vivado.

Refer to each project for its specific required modules.

Testbench for all modules and verification in the Vivado simulator.

Be prepared to explain your Verilog description and simulation results in a clear and logical

manner, and answer questions about your design from your lab TA at checko

Once you complete the above items, demonstrate your implementation on the Basys board

to your lab TA

Pay attention to projects and for the requirements on board implementation.

ProjectSpecific Checko

Requirements

Simple ALU calculator

Controller FSM module.

Datapath modules: Verilog description of all datapath components in your revised highlevel

design from the first milestone.

Toplevel module: Toplevel Verilog module describing connections between datapath compo

nents and controller.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock