Question: I need help please in designing a 32-bit ALU in Verilog that takes as input 32-bit input A, 32-bit input B, 2-bit OpCode S0 and

I need help please in designing a 32-bit ALU in Verilog that takes as input 32-bit input A, 32-bit input B, 2-bit OpCode S0 and S1, and performs the required operation yielding 32-bit output F. In addition, to the test bench.

Please include a brief explanation and comments in the written code and screenshots please

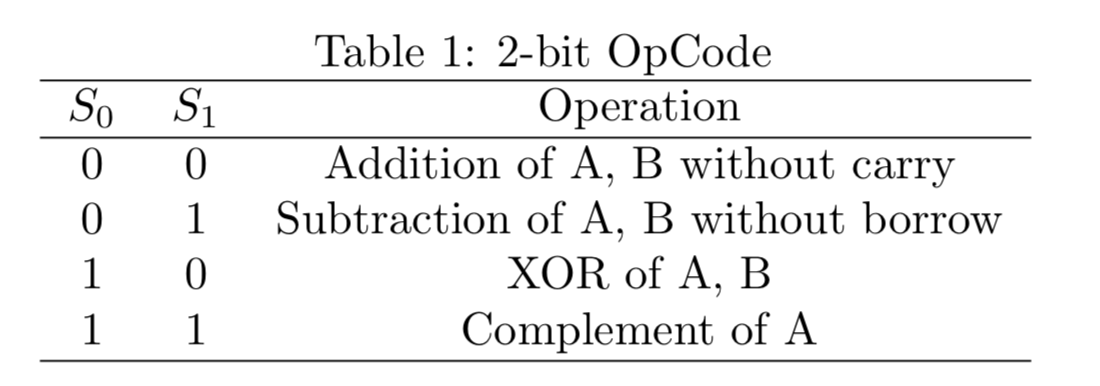

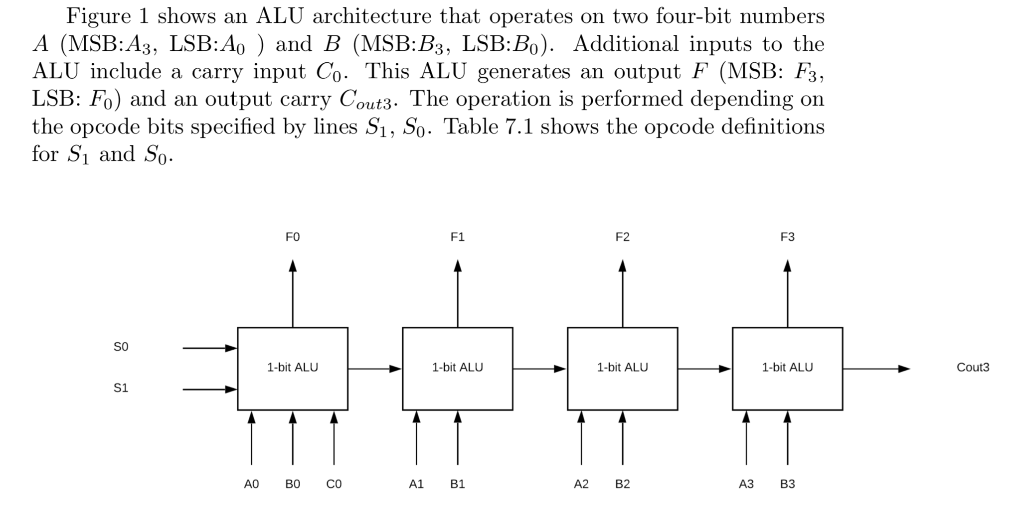

So Table 1: 2-bit OpCode Operation Addition of A, B without carry Subtraction of A, B without borrow XOR of A, B Complement of A Si 0 1 0 1 0 1 1 Figure 1 shows an ALU architecture that operates on two four-bit numbers A (MSB:A3, LSB:A0 ) and B (MSB:B3, LSB:B). Additional inputs to the ALU include a carry input Co. This ALU generates an output F (MSB: F3, LSB: Fo) and an output carry Cout3. The operation is performed depending on the opcode bits specified by lines Si, So. Table 7.1 shows the opcode definitions for Sand So. 1-16 ALL 1-bit ALU 1-bit ALU 1-bit ALU 1-bit ALU Cout3 1-bie ALU 1 1 1 1 1 A2B2 A3 B3

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts