Question: I need to do this as a code in Vivado HLX Editions (Xilinx): (15 points( VHDL Model for the ALU: This model has two data

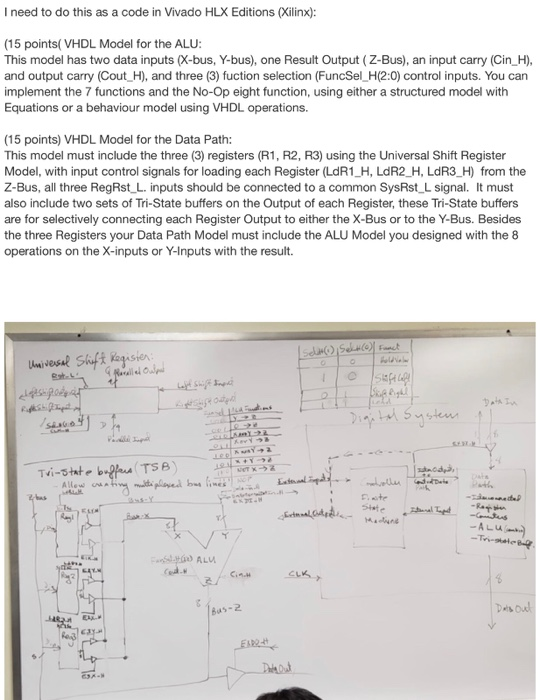

I need to do this as a code in Vivado HLX Editions (Xilinx): (15 points( VHDL Model for the ALU: This model has two data inputs (X-bus, Y-bus), one Result Output (Z-Bus), an input carry (Cin_ H), and output carry (Cout H), and three (3) fuction selection (FuncSel H(2:0) control inputs. You can implement the 7 functions and the No-Op eight function, using either a structured model with Equations or a behaviour model using VHDL operations. (15 points) VHDL Model for the Data Path This model must include the three (3) registers (R1, R2, R3) using the Universal Shift Register Model, with input control signals for loading each Register (LdR1_H, LdR2 H, LdR3 H) from the Z-Bus, all three RegRst L inputs should be connected to a common SysRst L signal. It must also include two sets of Tri-State buffers on the Output of each Register, these Tri-State buffers are for selectively connecting each Register Output to either the X-Bus or to the Y-Bus. Besides the three Registers your Data Path Model must include the ALU Model you designed with the 8 operations on the X-inputs or Y-Inputs with the result. n system 2 2

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts