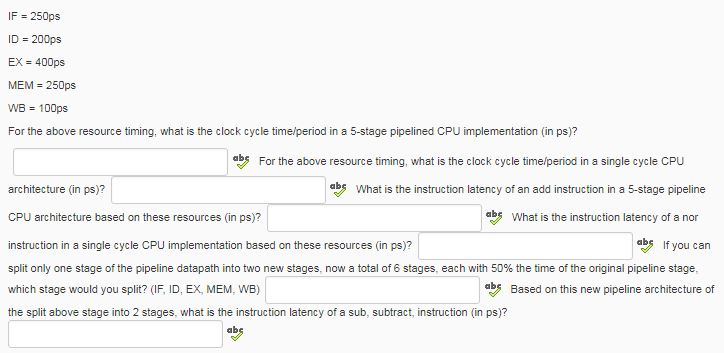

Question: IF = 25Ops ID = 200ps EX = 400ps MEM = 250ps WB = 100ps For the above resource timing, what is the clock cycle

IF = 25Ops ID = 200ps EX = 400ps MEM = 250ps WB = 100ps For the above resource timing, what is the clock cycle timeperiod in a 5-stage pipelined CPU implementation (in ps)? abs For the above resource timing, what is the clock cycle timeliperiod in a single cycle CPU architecture (in ps)? abs What is the instruction latency of an add instruction in a 5-stage pipeline CPU architecture based on these resources (in ps)? abs what is the instruction latency of a nor instruction in a single cycle CPU implementation based on these resources in ps)? abs. If you can split only one stage of the pipeline datapath into two new stages, now a total of 6 stages, each with 50% the time of the original pipeline stage, which stage would you split? (IF, ID, EX, MEM, WB) abs Based on this new pipeline architecture of the split above stage into 2 stages, what is the instruction latency of a sub, subtract, instruction (in ps)? abs

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts