Question: I'm not sure about the answers Consider an Intel 8086-based system with a 16-bit external data bus. The even ( which is active low), while

I'm not sure about the answers

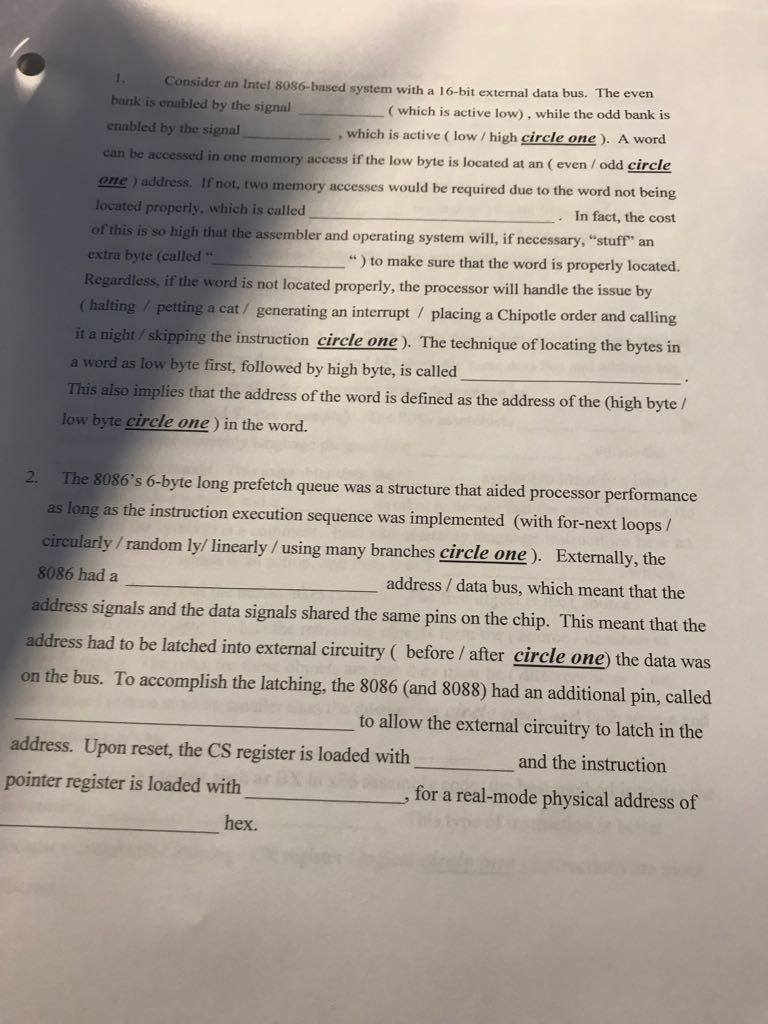

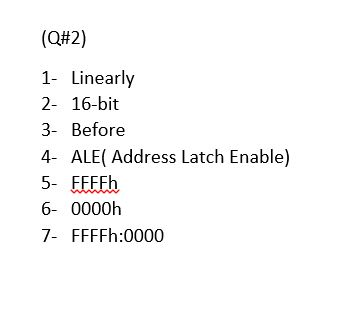

Consider an Intel 8086-based system with a 16-bit external data bus. The even ( which is active low), while the odd bank is , which is active ( low / high circle one). A word emory access if the low byte is located at an (even / odd circle f not, two memory accesses would be required due to the word not being . In fact, the cost bank is enabled by the signal enabled by the signal can be accessed in one m one address. I located properly, which is called of this is so high that the assembler and operating system will, if necessary, "stuff" an extra byte (called " Regardless, if the word is not located properly, the processor will handle the issue by (halting / petting a cat / generating an interrupt / placing a Chipotle order and calling it a night/skipping the instruction a word as low byte first, followed by high byte, is called This also implies that the address of the word is defined as the address of the (high byte / ) to make sure that the word is properly located. it a night / skipping the instruction circle one). The technique of locating the bytes in low byte circle one) in the word. 2. 2. The 8086's 6-byte long prefetch queue was a structure that aided processor performance as long as the instruction execution sequence was implemented (with for-next loops circularly /random ly/ linearly / using many branches circle one). Externally, the 8086 had a address / data bus, which meant that the address signals and the data signals shared the same pins on the chip. This meant that the address had to be latched into external circuitry ( before / after circle one the data was on the bus. To accomplish the latching, the 8086 (and 8088) had an additional pin, called to allow the external circuitry to latch in the address. Upon reset, the CS register is loaded withand the instruction pointer register is loaded with for a real-mode physical address of hex

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts