Question: Implement a 4-to-1 MUX using NAND gates only. Implement the function f (a, b, c) = ? m(0, 2, 3, 4, 5, 7) usinga) A

Implement a 4-to-1 MUX using NAND gates only.

Implement the function f (a, b, c) = ? m(0, 2, 3, 4, 5, 7) usinga) A 3-to-8 binary decoder and an OR gate. b) A 8-to-1Multiplexer only ...c) A 4-to-1 multiplexer with additionalgates..

(Show how you use truth tables and logic circuits to derive youranswers)

-

Implement the following function using a 2-to-1 multiplexer andminimal number of additional NAND gates. Show the truth table usedto derive your circuit.

g = ab + b^ c^

-

Implement the function f (w1, w2 , w3 ) = w1w2 + w2w3 + w1w2w3using the minimal

number of 2-input LUTs. Show the truth table implemented by eachLUT. (Apply Shannon?s expansion)

-

The AND-OR circuit that implements the following function, has acost of 14 (4 gates plus ten inputs).

f (x, y, z) = y ^z^ + x y + x y zApply Shannon?s expansion to derive a multi-level equivalentcircuit with

reduced cost, and state what is the new cost.

-

A priority 16-to-4 encoder has active LOW inputs and outputs. Ifthere are LOWs only on the following inputs what binary code willappear on the output?

a) LOWs on inputs 2,5, and 8

b) LOWs on inputs 1,4, and 7

c) LOWs on inputs 4,7, and 11

1

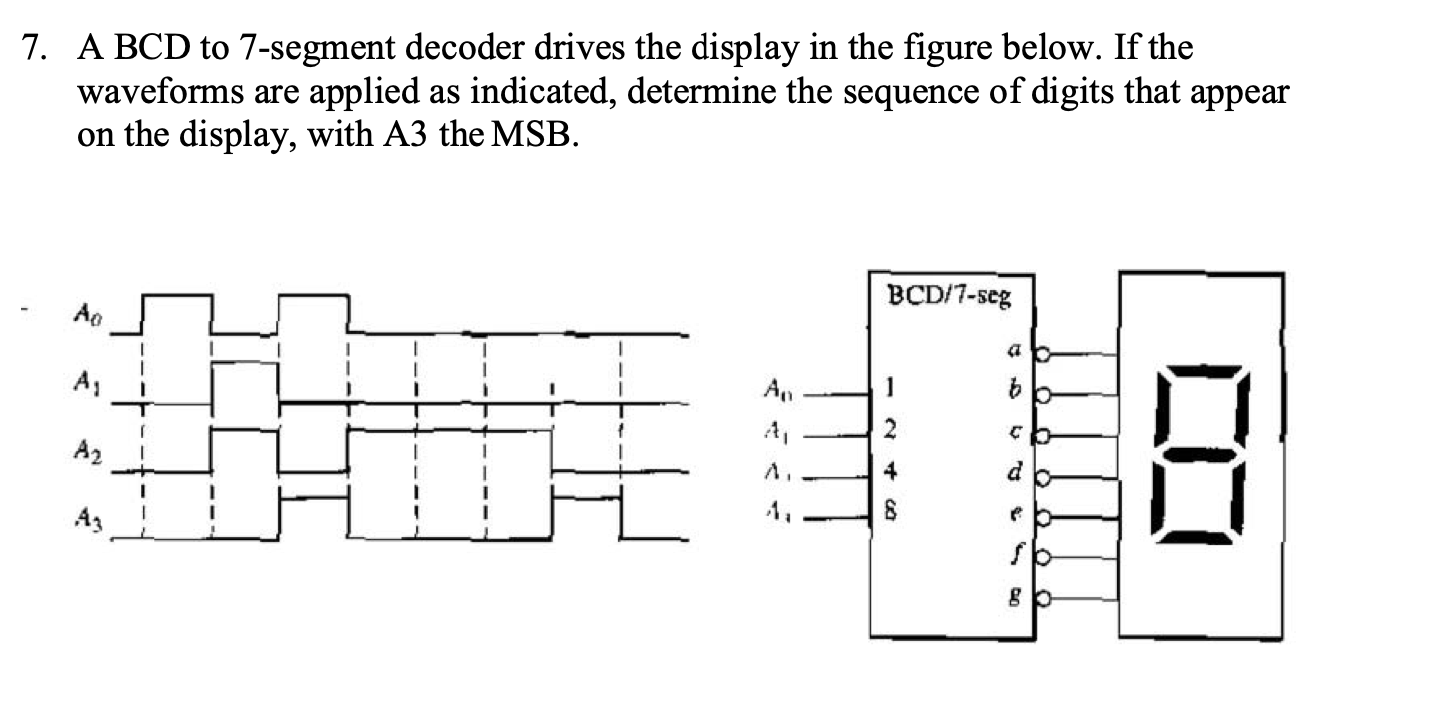

7. A BCD to 7-segment decoder drives the display in the figurebelow. If the waveforms are applied as indicated, determine thesequence of digits that appear on the display, with A3 the MSB.

7. A BCD to 7-segment decoder drives the display in the figure below. If the waveforms are applied as indicated, determine the sequence of digits that appear on the display, with A3 the MSB. Ao A A I An BCD/7-seg 4 ab bb cb eb sb 80

Step by Step Solution

3.54 Rating (154 Votes )

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts