Question: Implement the scheme below in verilog and carry out simulations to check the functionalities Description of the scheme + special requirements: The circuit above is

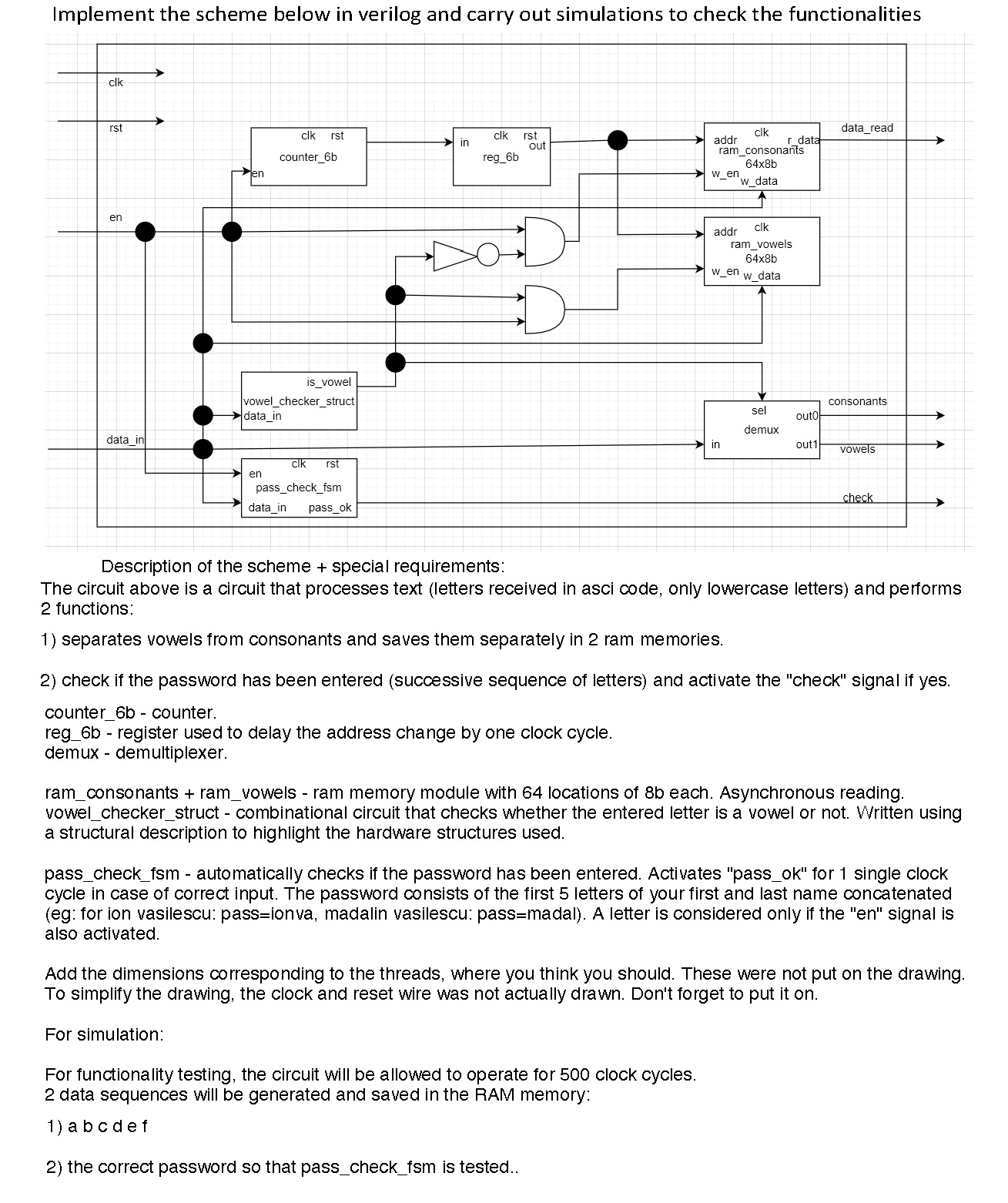

Implement the scheme below in verilog and carry out simulations to check the functionalities

Description of the scheme special requirements:

The circuit above is a circuit that processes text letters received in asci code, only lowercase letters and performs

functions:

separates vowels from consonants and saves them separately in ram memories.

check if the password has been entered successive sequence of letters and activate the "check" signal if yes.

counterb counter.

regb register used to delay the address change by one clock cycle.

demux demultiplexer.

ramconsonants ramvowels ram memory module with locations of each. Asynchronous reading.

vowelcheckerstruct combinational circuit that checks whether the entered letter is a vowel or not. Written using

a structural description to highlight the hardware structures used.

passcheckfsm automatically checks if the password has been entered. Activates "passok for single clock

cycle in case of correct input. The password consists of the first letters of your first and last name concatenated

eg: for ion vasilescu: passionva, madalin vasilescu: passmadal A letter is considered only if the en signal is

also activated.

Add the dimensions corresponding to the threads, where you think you should. These were not put on the drawing.

To simplify the drawing, the clock and reset wire was not actually drawn. Don't forget to put it on

For simulation:

For functionality testing, the circuit will be allowed to operate for clock cycles.

data sequences will be generated and saved in the RAM memory:

abcdef

the correct password so that passcheckfsm is tested..

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock