Question: In this assignment we will be modifying the capacity of a cache which can replace the instruction ram ian our CPU design. Description Download this

In this assignment we will be modifying the capacity of a cache which can replace the instruction ram ian our CPU design.

Description

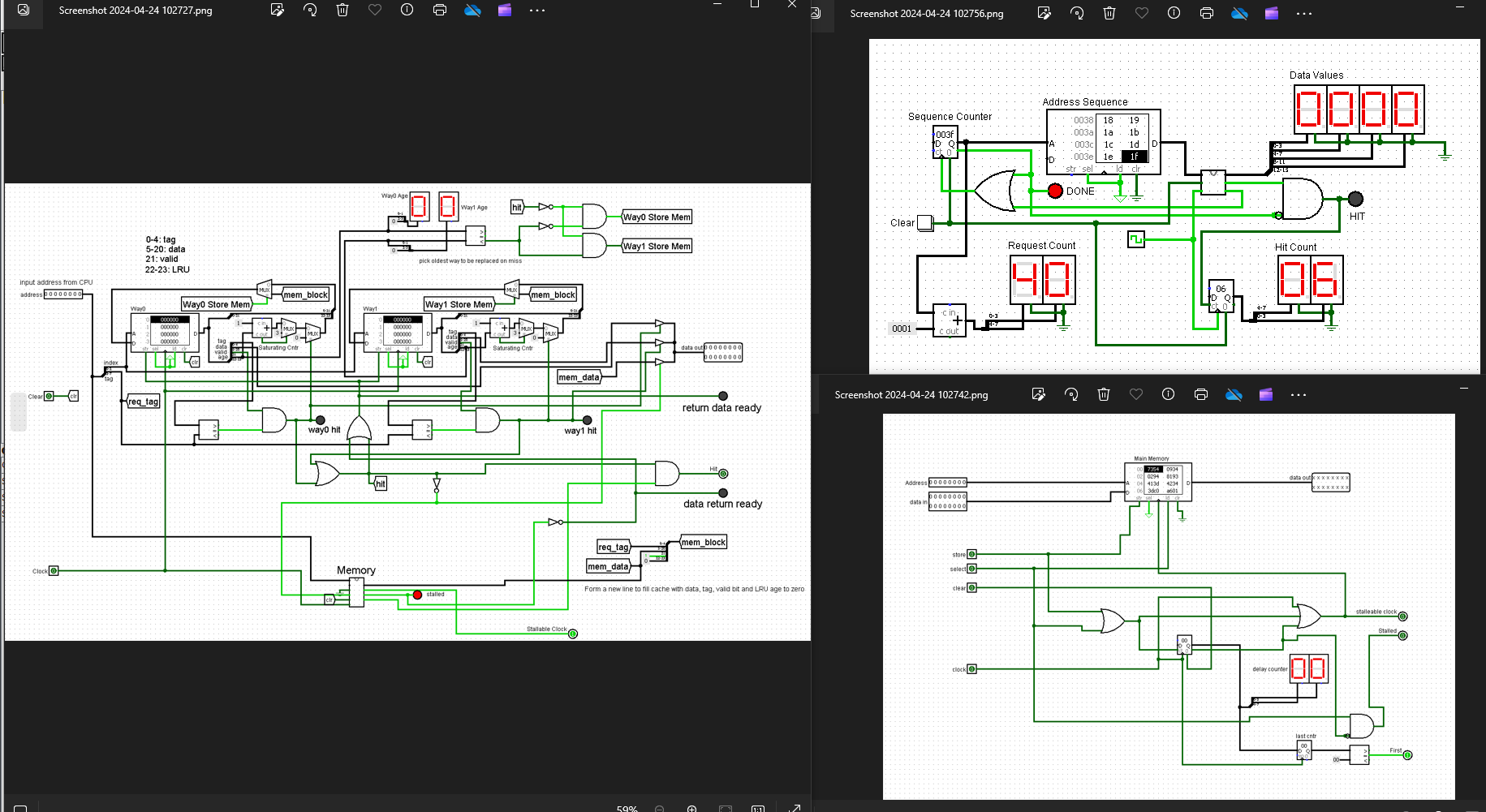

Download this Download thissolution package. Open the readcache.circ from the package. It contains three circuits:

A toplevel Main circuit, which provides circuity that feeds a sequence of memory addresses to the cache.

An AssocCache circuit, which implements a way bit block associative cache, with LRU replacement policy.

A Memory circuit, which models the main memory where bytes x bit data is stored. Misses from the associative cache are retrieved from here and stored to the cache.

Load the Address Sequence ram in the Main circuit with the AssocAddrsSeq.txt image. Load the Main Memory ram in the Memory circuit with the AssocmemData.txt image be careful here to load the correct instance of the Memory ram with the image; do so by double clicking on the embedded instance of the circuits, not the one in side panel Run the clock until Done led in the Main circuit goes high. Verify that you achieve a hit rate of

Familiarize yourself with the circuit. Notice how we are assigning bits to Tag, Data, Valid and Age for each entry in the cache.

Objective

Increase the capacity of the Associative Cache by x There are multiple ways of doing this. What is the resultant hit rate? Add the circuit to your assignment solution.

Objective

Modify the Address Sequence to generate an exact hit rate on the final circuit. There are lots of ways of doing this. Save your modified Address Sequence ram content and add to your assignment solution.

Zip the two files and submit it as the solution.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock