Question: In this lab, you are going to design a 4-bit shift register with parallel load by using synchronously resettable D flip-flops. This register will

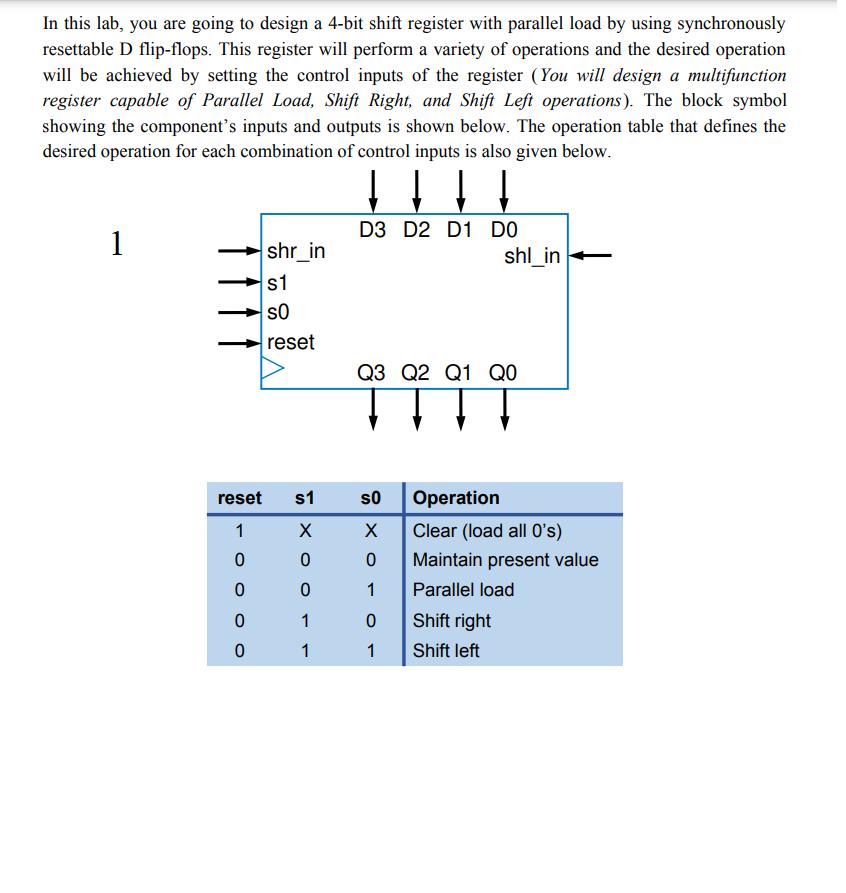

In this lab, you are going to design a 4-bit shift register with parallel load by using synchronously resettable D flip-flops. This register will perform a variety of operations and the desired operation will be achieved by setting the control inputs of the register (You will design a multifunction register capable of Parallel Load, Shift Right, and Shift Left operations). The block symbol showing the component's inputs and outputs is shown below. The operation table that defines the desired operation for each combination of control inputs is also given below. D3 D2 D1 DO 1 reset 1 0 0 0 0 shr_in s1 SO reset s1 X 0 0 1 1 Q3 Q2 Q1 QO 7777 so X 0 1 0 1 shl_in Operation Clear (load all 0's) Maintain present value Parallel load Shift right Shift left

Step by Step Solution

3.38 Rating (154 Votes )

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts