Question: In this problem, you will design a 4-bit 2's complement negator (without overflow detection). Every four cycles, the machine will take in 4 1-bit

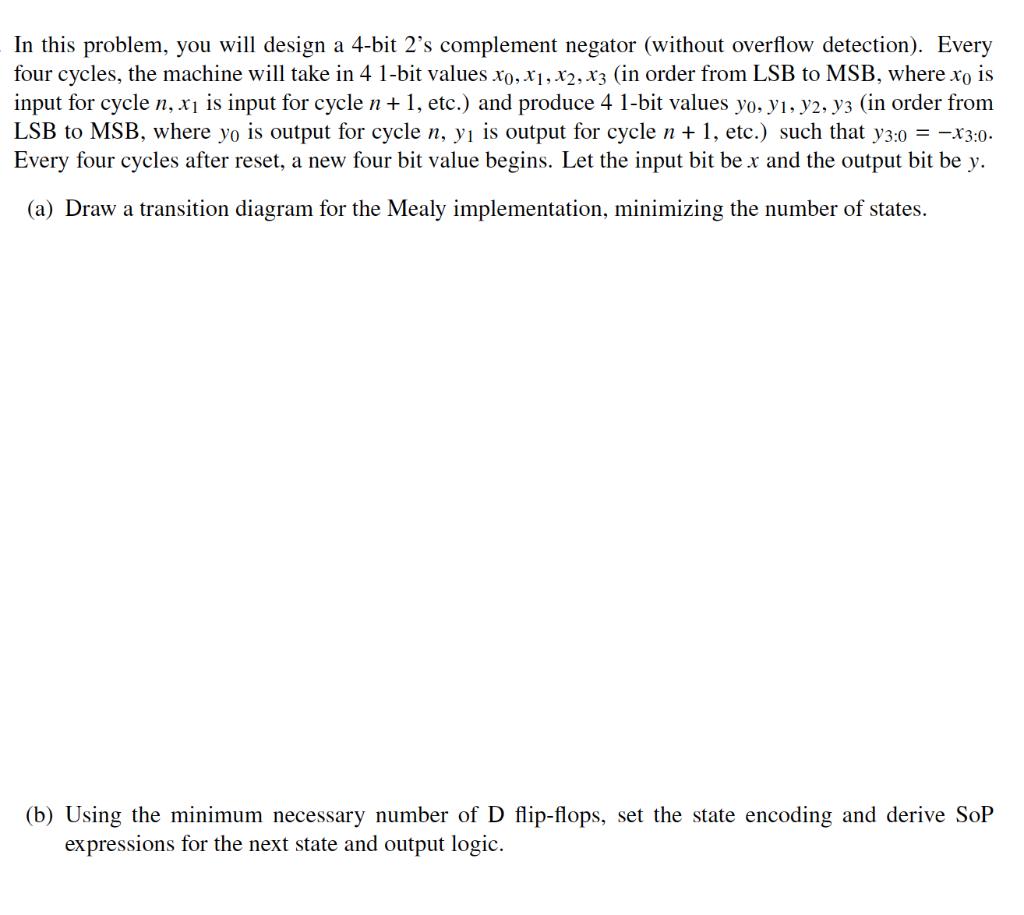

In this problem, you will design a 4-bit 2's complement negator (without overflow detection). Every four cycles, the machine will take in 4 1-bit values x0, x1, x2, x3 (in order from LSB to MSB, where xo is input for cycle n, x is input for cycle n+1, etc.) and produce 4 1-bit values yo, y1, y2, y3 (in order from LSB to MSB, where yo is output for cycle n, y is output for cycle n + 1, etc.) such that y3:0 = -x3:0. Every four cycles after reset, a new four bit value begins. Let the input bit be x and the output bit be y. (a) Draw a transition diagram for the Mealy implementation, minimizing the number of states. (b) Using the minimum necessary number of D flip-flops, set the state encoding and derive SoP expressions for the next state and output logic.

Step by Step Solution

3.38 Rating (157 Votes )

There are 3 Steps involved in it

Here are some minor suggestions for further improvement 1 Inheritance ... View full answer

Get step-by-step solutions from verified subject matter experts