Question: In Verilog If possible a testbench to test it This problem concerns the design of a 32-bit multiplier for floating point numbers (F1x251)* (F2x22) FX25

In Verilog

If possible a testbench to test it

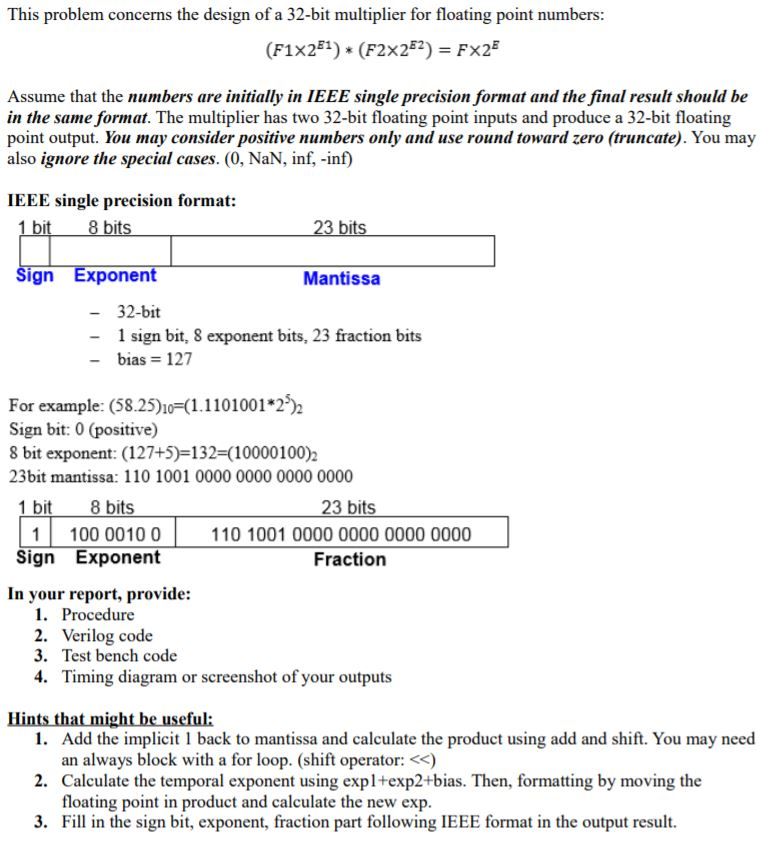

This problem concerns the design of a 32-bit multiplier for floating point numbers (F1x251)* (F2x22) FX25 Assume that the numbers are initially in IEEE single precision format and the final result should be in the same format. The multiplier has two 32-bit floating point inputs and produce a 32-bit floating point output. You may consider positive numbers only and use round toward zero (truncate). You may also ignore the special cases. (0, NaN, inf, -inf) IEEE single precision format: ign Exponen Mantissa 32-bit 1 sign bit, 8 exponent bits, 23 fraction bits bias 127 For example: (58.25)10 (1.1101001*2)2 Sign bit: 0 (positive) 8 bit exponent: (12745)=132-(10000100)2 23bit mantissa: 110 1001 0000 0000 0000 0000 1 bit 23 bits 110 1001 0000 0000 0000 0000 Fraction 8 bits 100 0010 0 Sign Exponent In your report, provide: 1. Procedure 2. Verilog code 3. Test bench code 4. Timing diagram or screenshot of your outputs 1. Add the implici 1 back to mantissa and calculate the product using add and shift. You may need 2. Calculate the temporal exponent using expl+exp2+bias. Then, formatting by moving the 3. an always block with a for loop. (shift operator:

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts