Question: Instruction Set Architecture Instruction Encoding In the RSC ISA, every i nstruction has a binary encoding with fixed l ength. This encoding allocates fixedlength fields

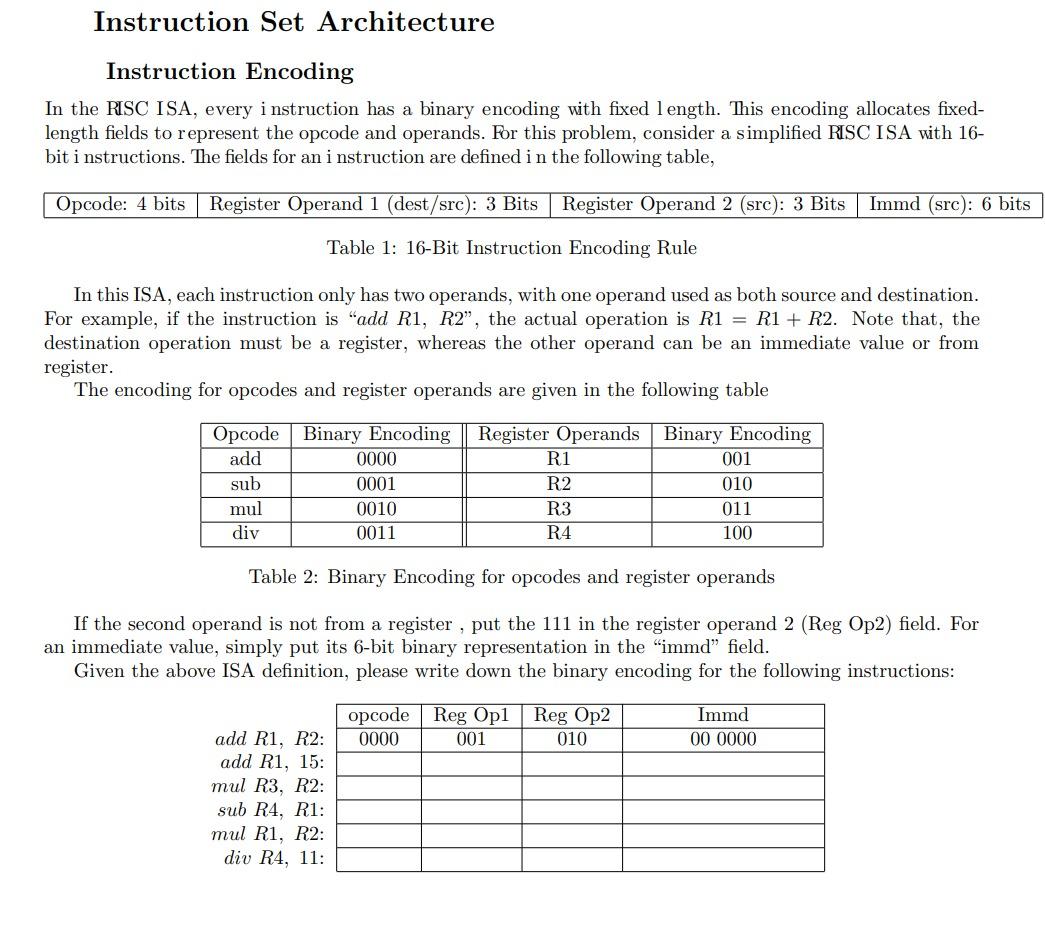

Instruction Set Architecture Instruction Encoding In the RSC ISA, every i nstruction has a binary encoding with fixed l ength. This encoding allocates fixedlength fields to represent the opcode and operands. For this problem, consider a simplified RISC ISA with 16bit i nstructions. The fields for an i nstruction are defined in the following table, \begin{tabular}{|l|l|l|l|l|} \hline Opcode: 4 bits & Register Operand 1 (dest/src): 3 Bits & Register Operand 2 (src): 3 Bits & Immd (src): 6 bit \\ \hline \end{tabular} Table 1: 16-Bit Instruction Encoding Rule In this ISA, each instruction only has two operands, with one operand used as both source and destination. For example, if the instruction is "add R1,R2 ", the actual operation is R1=R1+R2. Note that, the destination operation must be a register, whereas the other operand can be an immediate value or from register. The encoding for opcodes and register operands are given in the following table Table 2: Binary Encoding for opcodes and register operands If the second operand is not from a register, put the 111 in the register operand 2 (Reg Op2) field. For an immediate value, simply put its 6-bit binary representation in the "immd" field. Given the above ISA definition, please write down the binary encoding for the following instructions

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts