Question: It would be nice if there're explanations too. Exercise 4 Stable signals Consider the full adder circuit below and assume the given assignments for the

It would be nice if there're explanations too.

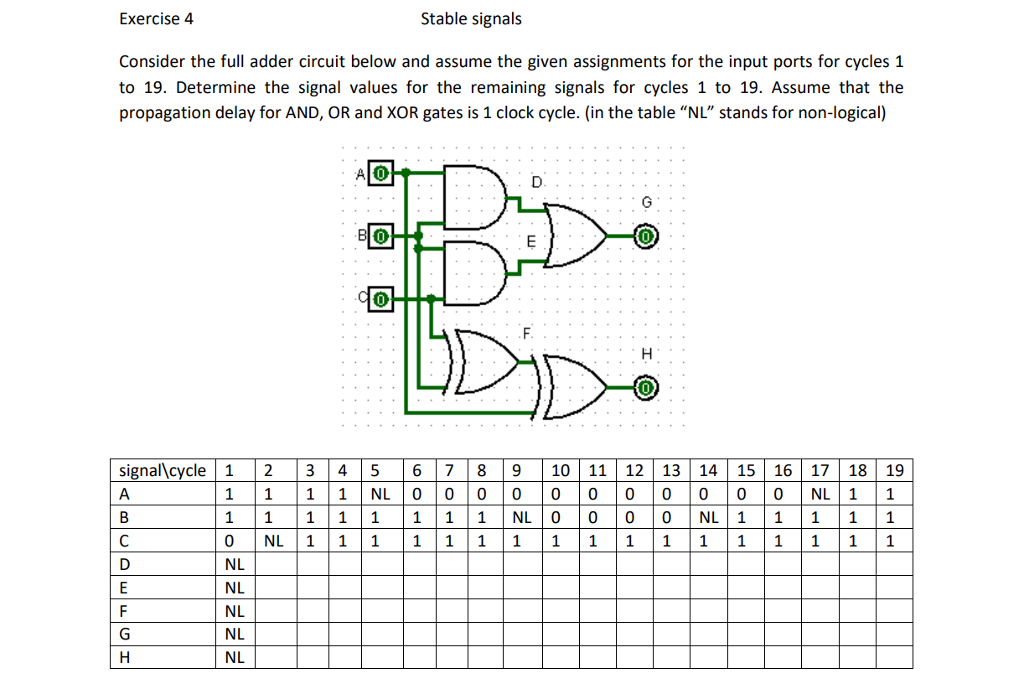

Exercise 4 Stable signals Consider the full adder circuit below and assume the given assignments for the input ports for cycles 1 to 19. Determine the signal values for the remaining signals for cycles 1 to 19. Assume that the propagation delay for AND, OR and XOR gates is 1 clock cycle. (in the table "NL" stands for non-logical) signal|cycle 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 NL RuI NL NL NL NL 1) Exercise 4 Stable signals Consider the full adder circuit below and assume the given assignments for the input ports for cycles 1 to 19. Determine the signal values for the remaining signals for cycles 1 to 19. Assume that the propagation delay for AND, OR and XOR gates is 1 clock cycle. (in the table "NL" stands for non-logical) signal|cycle 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 NL RuI NL NL NL NL 1)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts