Question: Iwant the answer and Explain it The following module definition is for a negative-edge triggered D flip-flop with Asynchronous RESET. nodule D.FF (D,CLK,RESET,Q), Choose the

Iwant the answer and Explain it

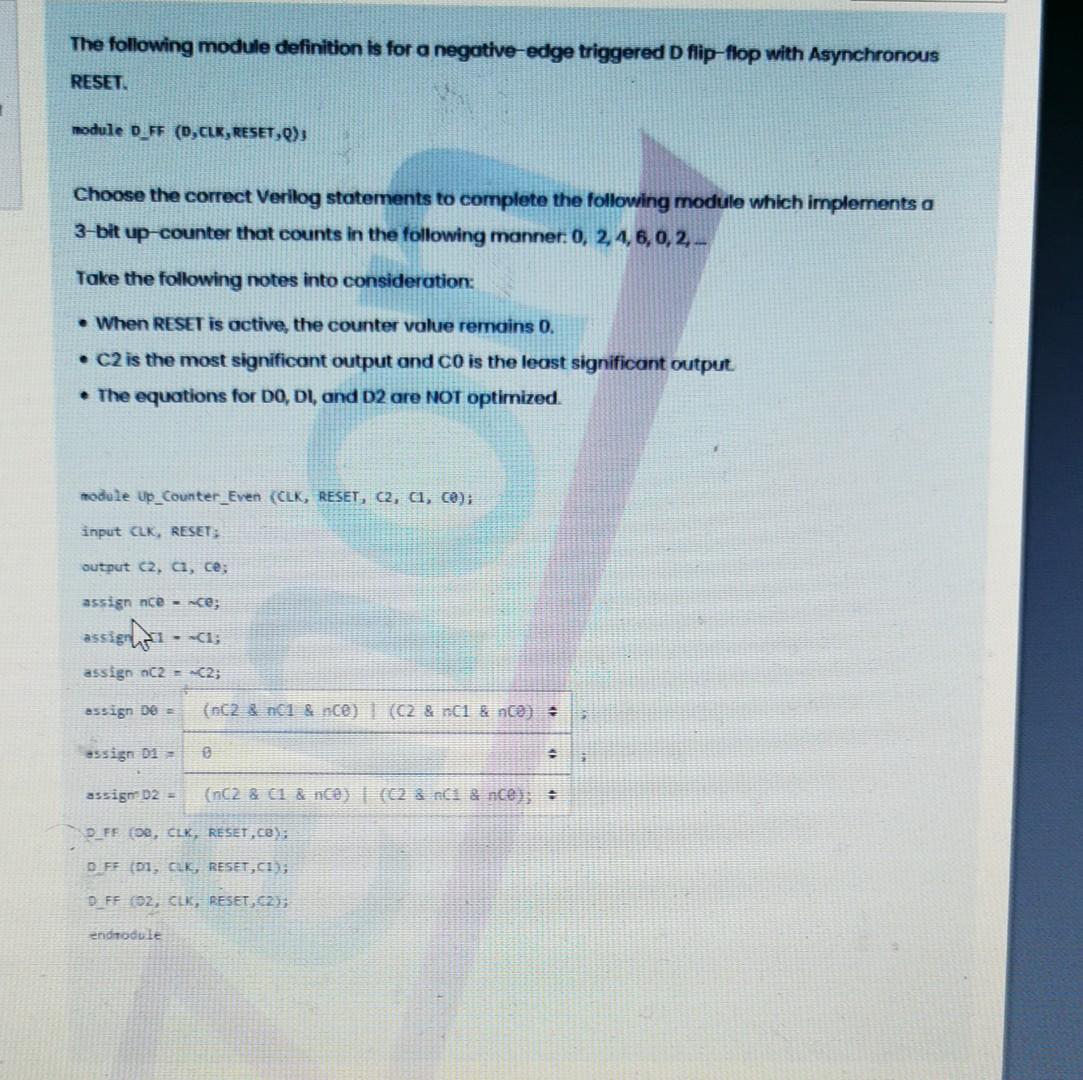

The following module definition is for a negative-edge triggered D flip-flop with Asynchronous RESET. nodule D.FF (D,CLK,RESET,Q), Choose the correct Verilog statements to complete the following module which implements a 3-bit up-counter that counts in the following manner: 0,2,4,6,0,2, Take the following notes into consideration: - When RESET is active, the counter volue remains 0. - C2 is the most significant output and CO is the least significant output. - The equations for DO, DI, and D2 are NOT optimized. module Up_Counter_Even (CLK, RESET, C2, C, C) ); input CLK, RESET; output C2,Cl,Ce; assign nce - ace; assignti - Cl1 assign nC2 =2; assign D=(nC2&nC1&nC)(C2&nC1&nC)= assign 01= assigm D2 =(nC2&C1&n()(C2&nC1 \& nC);= D_FE ( (, CLK, RESET, CO); Q. FF (D), CuK, RESET, Cl); D.FF (02, CLK, RESET, CZ); endrodule

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts