Question: Keep in mind that branch instruction takes three clock cycles as shown in RISC - V architecture ( IMPORTANT ) . Consider the following RISC

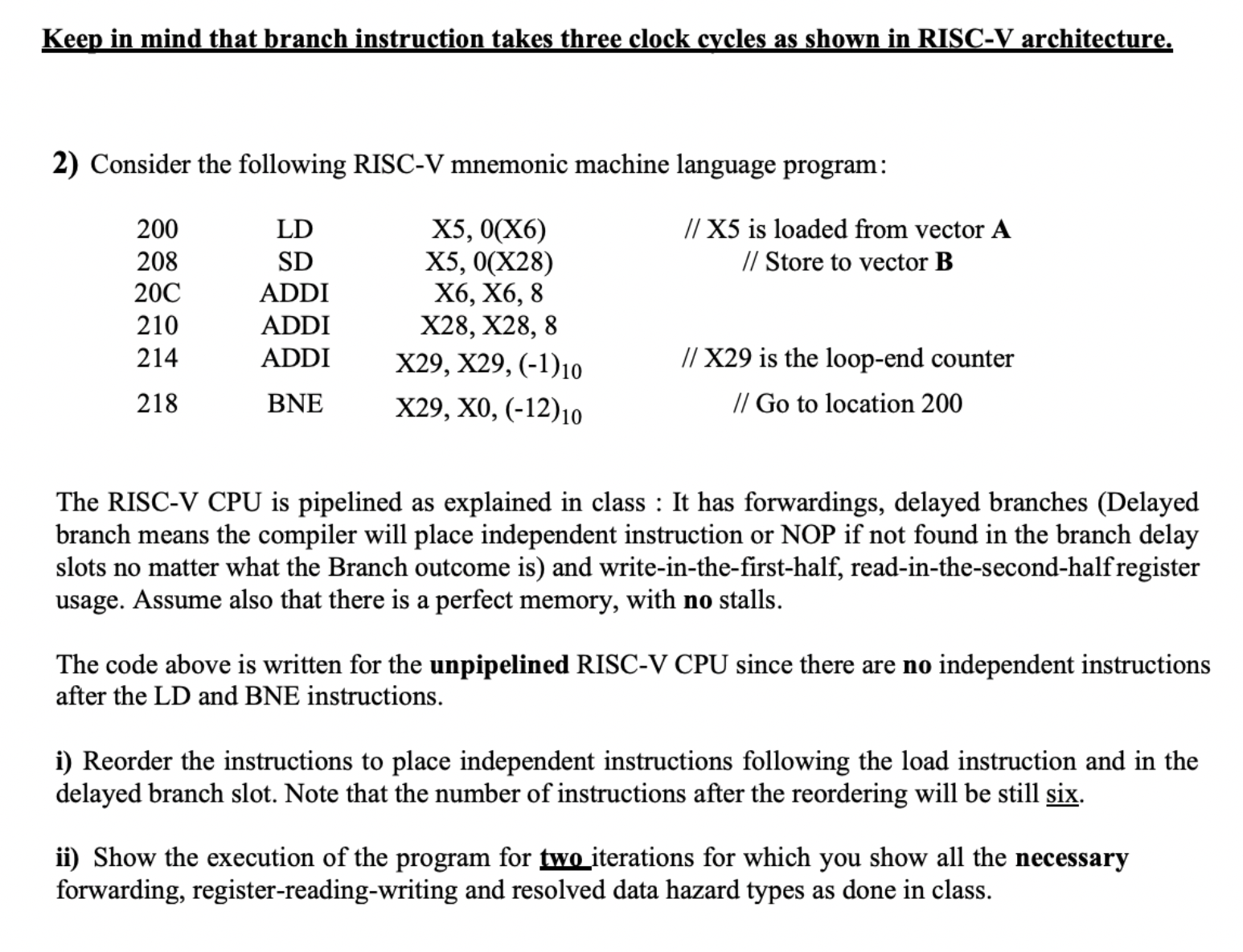

Keep in mind that branch instruction takes three clock cycles as shown in RISCV architecture IMPORTANT

Consider the following RISCV mnemonic machine language program:

The RISCV CPU is pipelined as explained in class : It has forwardings, delayed branches Delayed

branch means the compiler will place independent instruction or NOP if not found in the branch delay

slots no matter what the Branch outcome is and writeinthefirsthalf, readinthesecondhalf register

usage. Assume also that there is a perfect memory, with no stalls.

The code above is written for the unpipelined RISCV CPU since there are no independent instructions

after the LD and BNE instructions.

i Reorder the instructions to place independent instructions following the load instruction and in the

delayed branch slot. Note that the number of instructions after the reordering will be still six.

ii Show the execution of the program for two iterations for which you show AND EXPLAIN all the necessary

forwarding, registerreadingwriting and resolved data hazard types as done in class.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock