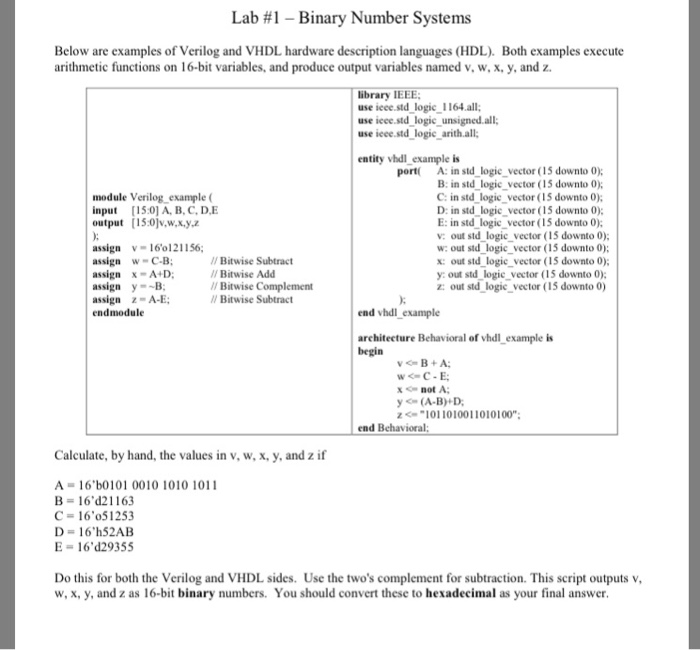

Question: Lab #1-Binary Number Systems Below are examples of Verilog and VHDL hardware description languages (HDL). Both examples execute arithmetic functions on 16-bit variables, and produce

Lab #1-Binary Number Systems Below are examples of Verilog and VHDL hardware description languages (HDL). Both examples execute arithmetic functions on 16-bit variables, and produce output variables named v, w,x,y, and z. library IEEE use ieee.std logic 1164.all; use ieee.std logic unsigned.all; use ieee.std logie arith.all: entity vhdl example is port A: in std logic_vector (15 downto 0); B: in std logic vector (15 downto 0) C: in std logic vector (15 downto 0) D: in std logic vector (15 downto 0) E: in std logic vector (15 downto 0) v: out std logic vector (15 downto 0); w: out std logic vector (15 downto 0) x: out std logie vector (15 downto 0); y: out std logie vector (15 downto 0) z: out std logic vector (15 downto 0) module Verilog, example input [15.0] A, B, C, D,E output [15.0v.w,x.y.z assign -1612156; assign w-C-B assign A+D assign y- assign z A-E endmodule // Bitwise Subtract // Bitwise Add // Bitwise Complement / Bitwise Subtract end vhdl example architecture Behavioral of vhdl example is begin 1011010011010100" end Behavioral Calculate, by hand, the values in v, w, x, y, and z if A 16'b0101 0010 1010 1011 B- 16'd21163 C- 16 051253 D- 16'h52AB E- 16'd29355 Do this for both the Verilog and VHDL sides. Use the two's complement for subtraction. This script outputs v w, x, y, and z as 16-bit binary numbers. You should convert these to hexadecimal as your final

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts