Question: Linear Paging We use Simulator paging - linear - translate.py to study how the address translation work with the linear paging table. We ran a

Linear Paging

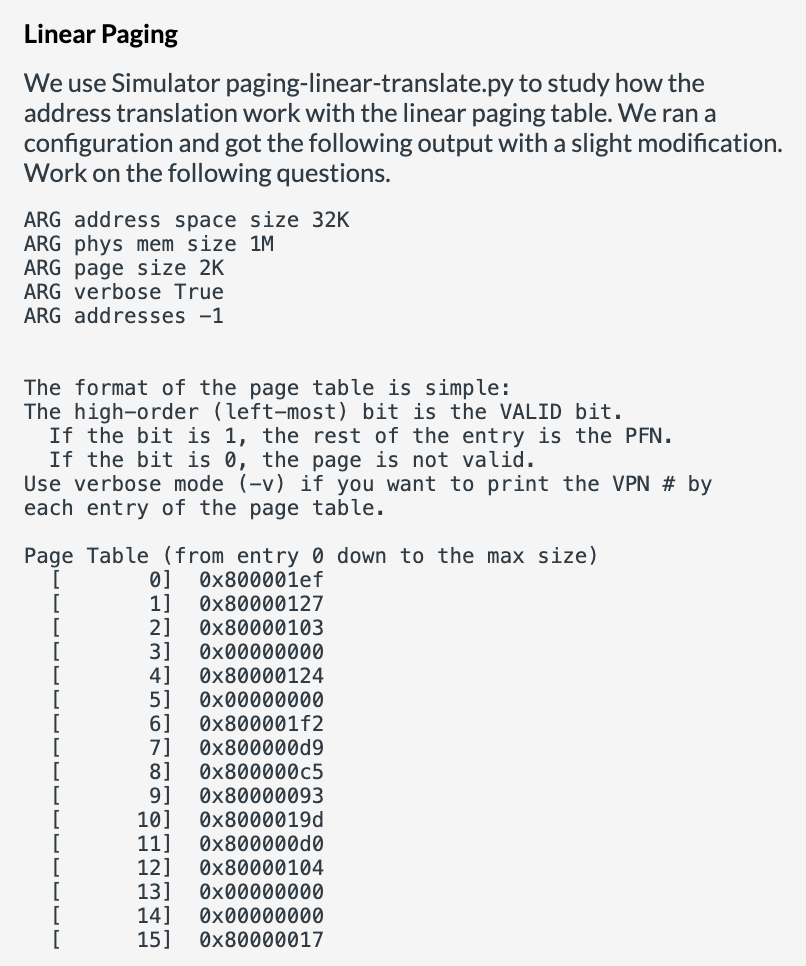

We use Simulator paginglineartranslate.py to study how the

address translation work with the linear paging table. We ran a

configuration and got the following output with a slight modification.

Work on the following questions.

ARG address space size K

ARG phys mem size M

ARG page size K

ARG verbose True

ARG addresses

The format of the page table is simple:

The highorder leftmost bit is the VALID bit.

If the bit is the rest of the entry is the PFN

If the bit is the page is not valid.

Use verbose mode v if you want to print the VPN # by

each entry of the page table.

Page Table from entry down to the max size

Given the answer in decimal format, so don't use hexidecimal or binary format for solutions in the four questions below. Given the configuration perform the configuration in the image for the four questions below.

For Virtual Address xehexadecimal fill in the blank its VPN virtual page number in decimal format.

For Virtual Address xchexadecimal if it is an invalid address, fill in the blank with otherwise fill in the blank with the mapped PFN physical frame number in decimal format.

For Virtual Address xahexadecimal if it is an invalid address, fill in the blank with otherwise fill in the blank with the mapped physical address in decimal format.

For Virtual Address xahexadecimal if it is an invalid address, fill in the blank with otherwise fill in the blank with the mapped physical address in decimal format.

For Virtual Address xf hexadecimal if it is an invalid address, fill in the blank with otherwise fill in the blank with the mapped physical address in decimal format.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock