Question: Logic Circuit Using a binary decoder with 1-hot logic, OR gate, and one additional component (i.e. gate or multiplexer), implement F = (m2, m4, m6,

Logic Circuit

Logic Circuit

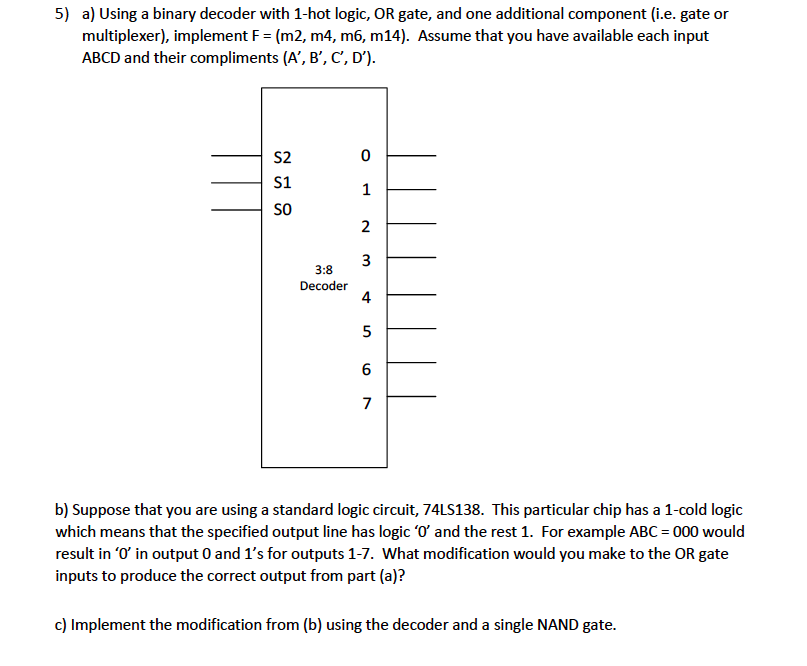

Using a binary decoder with 1-hot logic, OR gate, and one additional component (i.e. gate or multiplexer), implement F = (m2, m4, m6, ml4). Assume that you have available each input ABCD and their compliments (A', B', C', D'). Suppose that you are using a standard logic circuit, 74LS138. This particular chip has a 1-cold logic which means that the specified output line has logic '0' and the rest 1. For example ABC = 000 would result in '0' in output 0 and l's for outputs 1-7. What modification would you make to the OR gate inputs to produce the correct output from part (a)? Implement the modification from (b) using the decoder and a single NAND gate. Using a binary decoder with 1-hot logic, OR gate, and one additional component (i.e. gate or multiplexer), implement F = (m2, m4, m6, ml4). Assume that you have available each input ABCD and their compliments (A', B', C', D'). Suppose that you are using a standard logic circuit, 74LS138. This particular chip has a 1-cold logic which means that the specified output line has logic '0' and the rest 1. For example ABC = 000 would result in '0' in output 0 and l's for outputs 1-7. What modification would you make to the OR gate inputs to produce the correct output from part (a)? Implement the modification from (b) using the decoder and a single NAND gate

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts