Question: MICROPROGRAMMABLE CONTROL USING XILYNX. ONLY SOLVE IF YOU KNOW VHDL IMPLEMENTATION OF FPGAS USING XILYNX. USING XILYNX, DESIGN THE ROM, COUNTER, AND MUX AND SHOW

MICROPROGRAMMABLE CONTROL USING XILYNX. ONLY SOLVE IF YOU KNOW VHDL IMPLEMENTATION OF FPGAS USING XILYNX.

USING XILYNX, DESIGN THE ROM, COUNTER, AND MUX AND SHOW A STEP BY STEP EXPLANATION OF GETTING:

1. TOP LEVEL SCHEMATIC

2. STATE DIAGRAM FOR MICROCODE

3. MICROCODE WITH COMMENTS

4. WAVEFORM AND VERIFICATION

**DESCRIBE EVERY CRITICAL WINDOW IN THE SIMULATION TO VERIFY THE RESULTS

ONLY IF YOUR RESULT IS CORRECT AND PROVIDES EXPLANATIONS FOR EACH STEP TO HELP ME UNDERSTAND WHAT IS GOING ON, I WILL THUMBS UP.

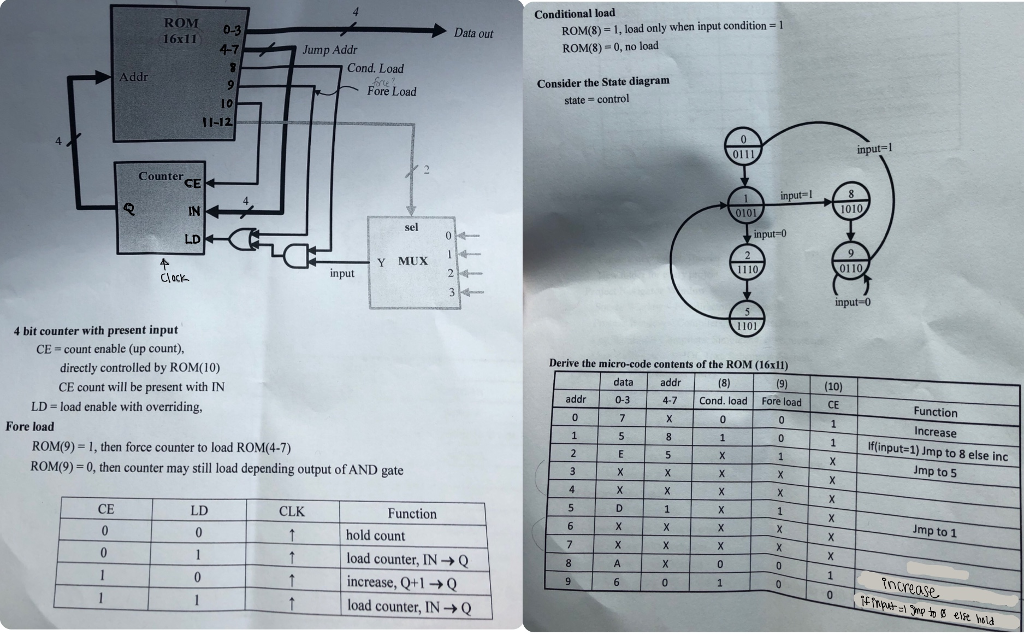

Conditional load ROM(8) -1, load only when input condition 1 ROM(8) 0, no load ROM 0-3 Data out 4-7Jump Addr Cond. Load Consider the State diagram state = control Addr 10 11-12 4. 011 Counter CE 1input l 0101 101 nput-o - LD Y MUX 1 011 110 input Clock nput-0 4 bit counter with present input CE- count enable (up count), directly controlled by ROM(10) CE count will be present with IN Derive the micro-code contents of the ROM (16xl1) data addr (8) (10) adr 0-34Cond.odFore load CE Function LD load enable with overriding, Increase Fore load 1 If(input-1) Jmp to 8 else inc ROM(9) 1, then force counter to load ROM(4-7) ROM(9)-0, then counter may still load depending output of AND gate mp to 5 CE LD CLK Function mp to 1 hold count load counter, IN Q increase, Q+1 Q load counter, IN-Q increose Conditional load ROM(8) -1, load only when input condition 1 ROM(8) 0, no load ROM 0-3 Data out 4-7Jump Addr Cond. Load Consider the State diagram state = control Addr 10 11-12 4. 011 Counter CE 1input l 0101 101 nput-o - LD Y MUX 1 011 110 input Clock nput-0 4 bit counter with present input CE- count enable (up count), directly controlled by ROM(10) CE count will be present with IN Derive the micro-code contents of the ROM (16xl1) data addr (8) (10) adr 0-34Cond.odFore load CE Function LD load enable with overriding, Increase Fore load 1 If(input-1) Jmp to 8 else inc ROM(9) 1, then force counter to load ROM(4-7) ROM(9)-0, then counter may still load depending output of AND gate mp to 5 CE LD CLK Function mp to 1 hold count load counter, IN Q increase, Q+1 Q load counter, IN-Q increose

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts