Question: MIPS 5 - Stage Pipeline and Reorder buffer simulator Consider the default setting given in the simulator. The following set of instruction: LD F 6

MIPS Stage Pipeline and Reorder buffer simulator

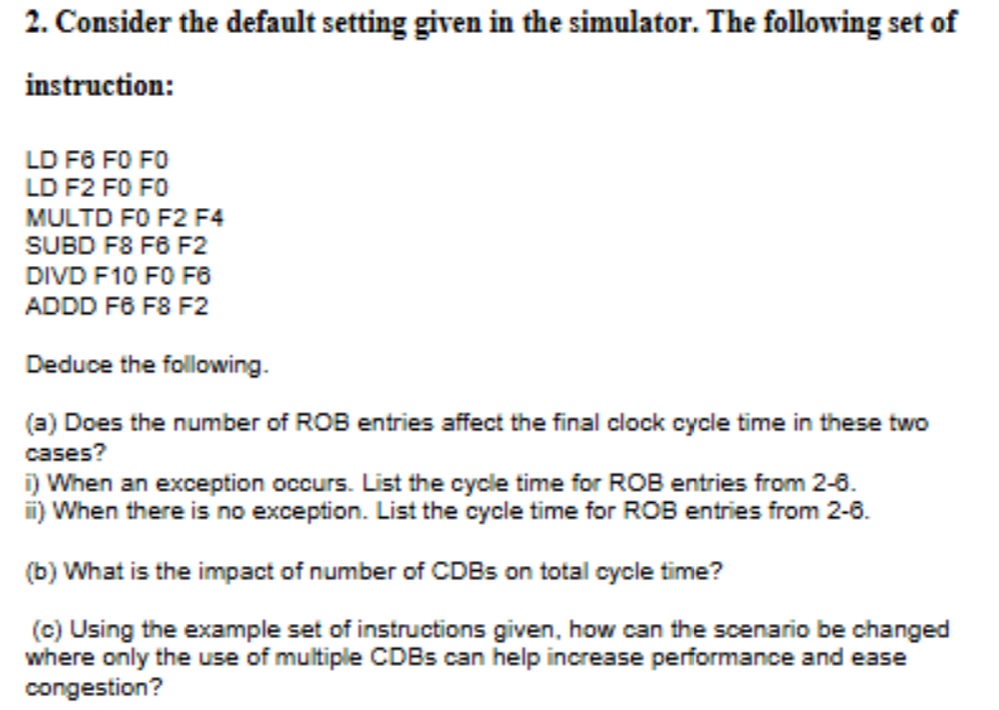

Consider the default setting given in the simulator. The following set of

instruction:

LD F F F

LD F F F

MULTD F F F

SUBD F F F

DIVD F F F

ADDD F F F

Deduce the following.

a Does the number of ROB entries affect the final clock cycle time in these two

cases?

i When an exception occurs. List the cycle time for ROB entries from

ii When there is no exception. List the cycle time for ROB entries from

b What is the impact of number of CDBs on total cycle time?

c Using the example set of instructions given, how can the scenario be changed

where only the use of multiple CDBs can help increase performance and ease

congestion?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock