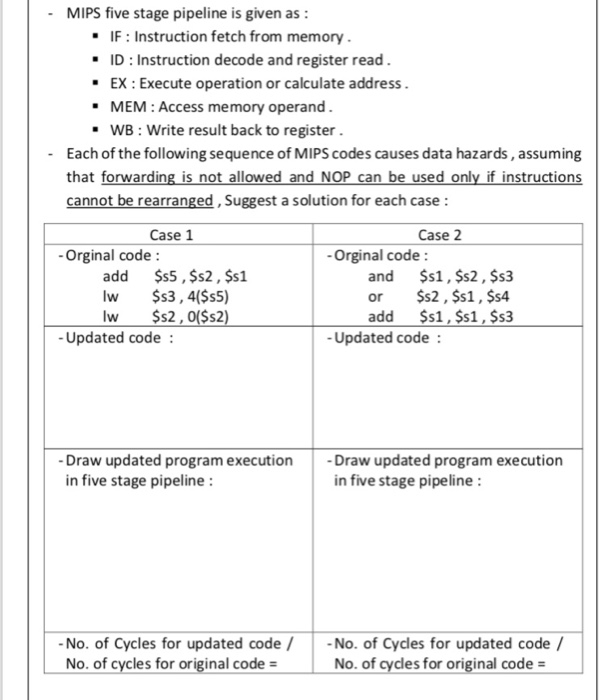

Question: - MIPS five stage pipeline is given as IF Instruction fetch from memory ID Instruction decode and register read EX Execute operation or calculate address

- MIPS five stage pipeline is given as IF Instruction fetch from memory ID Instruction decode and register read EX Execute operation or calculate address MEM: Access memory operand WB: Write result back to register Each of the following sequence of MIPS codes causes data hazards, assuming that forwarding is not allowed and NOP can be used only if instructions cannot be rearranged, Suggest a solution for each case - Case 1 Case 2 -Orginal code: and or add -Updated code: -Orginal code add $s5,Ss2, Ss1 lw $S3,4($s5) Iw 2, 0(Ss2) $s1, $s2, $s3 $s2, $s1, $s4 $s1, Ss1, Ss3 -Updated code: Draw updated program execution in five stage pipeline: Draw updated program execution in five stage pipeline No. of Cycles for updated codeNo. of Cycles for updated code / No. of cycles for original code - No. of cycles for original code

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts