Question: MIPS Processor Design Example Problem 2a (25 points): Suppose we have a 5-stage MIPS pipeline with all possible forwarding. Branches work as described up to

MIPS Processor Design

Example

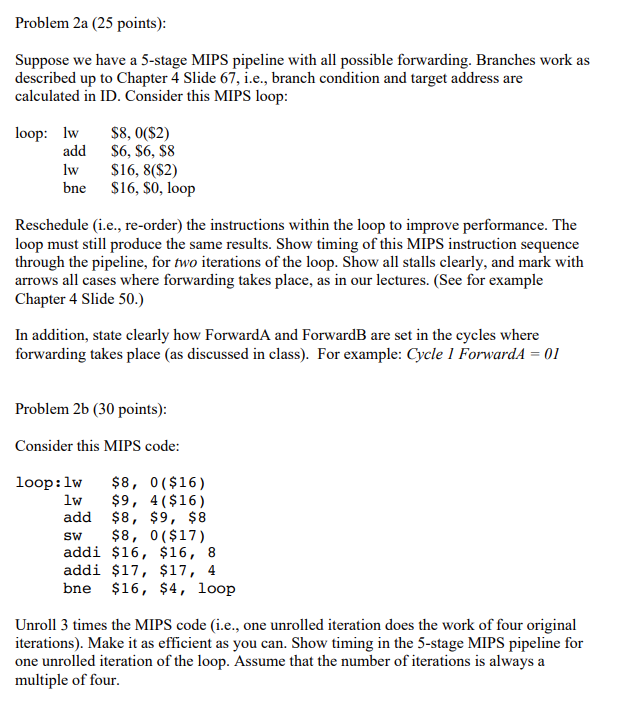

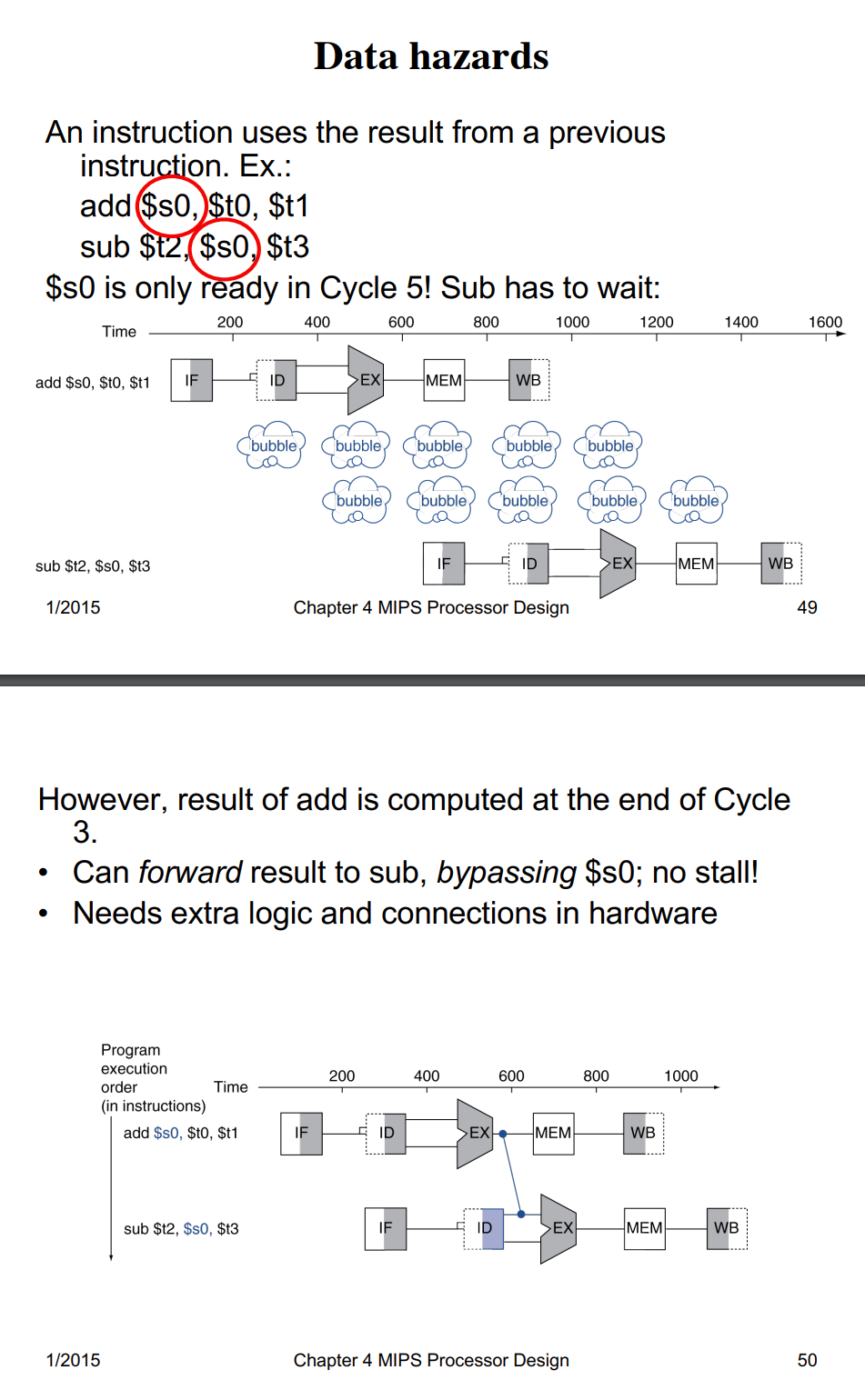

Problem 2a (25 points): Suppose we have a 5-stage MIPS pipeline with all possible forwarding. Branches work as described up to Chapter 4 Slide 67, i.e., branch condition and target address are calculated in ID. Consider this MIPS loop: loop: lw $8,0(82) add $6, $6, $8 lw $16, 8($2) bne $16, $0, loop Reschedule (i.e., re-order) the instructions within the loop to improve performance. The loop must still produce the same results. Show timing of this MIPS instruction sequence through the pipeline, for two iterations of the loop. Show all stalls clearly, and mark with arrows all cases where forwarding takes place, as in our lectures. (See for example Chapter 4 Slide 50.) In addition, state clearly how ForwardA and ForwardB are set in the cycles where forwarding takes place (as discussed in class). For example: Cycle 1 ForwardA = 01 Problem 2b (30 points): Consider this MIPS code: loop:lw $8, 0($16) lw $9, 4($16) add $8, $9, $8 sw $8, 0($17) addi $16, $16, 8 addi $17, $17, 4 bne $16, $4, loop Unroll 3 times the MIPS code (i.e., one unrolled iteration does the work of four original iterations). Make it as efficient as you can. Show timing in the 5-stage MIPS pipeline for one unrolled iteration of the loop. Assume that the number of iterations is always a multiple of four. Data hazards An instruction uses the result from a previous instruction. Ex.: add($s0,$t0,$t1 sub $t2, $s0, $t3 ( $s0 is only ready in Cycle 5! Sub has to wait: 200 400 600 800 1000 1200 1400 Time 1600 T add $80, $to, $t1 IF SID >EX MEM WB bubble ca bubble bubble bubble bubble bubble bubble bubble bubble bubble La sub $t2, $s0, $t3 IF 5 ID >EX MEM WB 1/2015 Chapter 4 MIPS Processor Design 49 However, result of add is computed at the end of Cycle 3. Can forward result to sub, bypassing $s0; no stall! Needs extra logic and connections in hardware . 200 400 600 800 1000 Program execution order Time (in instructions) add $s, $t0,$t1 IF ID SEX MEM WB sub $t2, $50, $t3 IF ID >EX MEM WB 1/2015 Chapter 4 MIPS Processor Design 50

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts