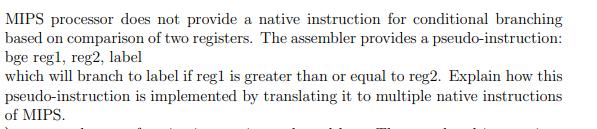

Question: MIPS processor does not provide a native instruction for conditional branching based on comparison of two registers. The assembler provides a pseudo-instruction: bge reg1,

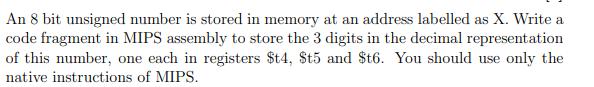

MIPS processor does not provide a native instruction for conditional branching based on comparison of two registers. The assembler provides a pseudo-instruction: bge reg1, reg2, label which will branch to label if reg1 is greater than or equal to reg2. Explain how this is implemented by translating it to multiple native instructions pseudo-instruction of MIPS. An 8 bit unsigned number is stored in memory at an address labelled as X. Write a code fragment in MIPS assembly to store the 3 digits in the decimal representation of this number, one each in registers $t4, $t5 and $t6. You should use only the native instructions of MIPS.

Step by Step Solution

3.37 Rating (147 Votes )

There are 3 Steps involved in it

The detailed ... View full answer

Get step-by-step solutions from verified subject matter experts