Question: More than one branch can be active simultaneously as only the probabilities of the next states are being computed e None of the above 6.

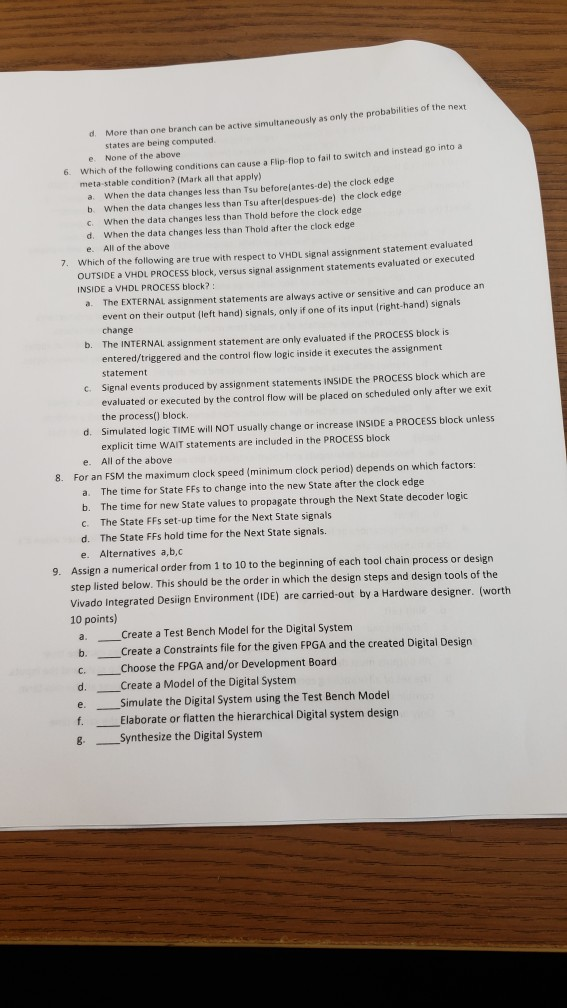

More than one branch can be active simultaneously as only the probabilities of the next states are being computed e None of the above 6. Which of the following conditions can cause a Flip flop to fail to switch and instead go into a meta-stable condition? (Mark all that apply) a When the data changes less than Tsu before antes-de) the clock edge b. When the data changes less than Tsu after despues-de) the clock edge c When the data changes less than Thold before the clock edge d. When the data changes less than Thold after the clock edge e. All of the above 7. Which of the following are true with respect to VHDL signal assignment statement evaluated OUTSIDE a VHDL PROCESS block, versus signal assignment statements evaluated or executed INSIDE a VHDL PROCESS block?! a The EXTERNAL assignment statements are always active or sensitive and can produce an event on their output (left hand) signals, only if one of its input right-hand) signals change b. The INTERNAL assignment statement are only evaluated if the PROCESS block is entered/triggered and the control flow logic inside it executes the assignment statement Signal events produced by assignment statements INSIDE the PROCESS block which are evaluated or executed by the control flow will be placed on scheduled only after we exit the process() block d. Simulated logic TIME will NOT usually change or increase INSIDE a PROCESS block unless explicit time WAIT statements are included in the PROCESS block e. All of the above 8. For an FSM the maximum clock speed (minimum clock period) depends on which factors: a. The time for State FFs to change into the new State after the clock edge b. The time for new State values to propagate through the Next State decoder logic C. The State FFs set-up time for the Next State signals d. The State FFs hold time for the Next State signals. e. Alternatives a,b,c 9. Assign a numerical order from 1 to 10 to the beginning of each tool chain process or design step listed below. This should be the order in which the design steps and design tools of the Vivado Integrated Design Environment (IDE) are carried out by a Hardware designer. (worth 10 points) Create a Test Bench Model for the Digital System b. Create a Constraints file for the given FPGA and the created Digital Design C. Choose the FPGA and/or Development Board Create a Model of the Digital System Simulate the Digital System using the Test Bench Model Elaborate or flatten the hierarchical Digital system design 8. Synthesize the Digital System Usai Bo More than one branch can be active simultaneously as only the probabilities of the next states are being computed e None of the above 6. Which of the following conditions can cause a Flip flop to fail to switch and instead go into a meta-stable condition? (Mark all that apply) a When the data changes less than Tsu before antes-de) the clock edge b. When the data changes less than Tsu after despues-de) the clock edge c When the data changes less than Thold before the clock edge d. When the data changes less than Thold after the clock edge e. All of the above 7. Which of the following are true with respect to VHDL signal assignment statement evaluated OUTSIDE a VHDL PROCESS block, versus signal assignment statements evaluated or executed INSIDE a VHDL PROCESS block?! a The EXTERNAL assignment statements are always active or sensitive and can produce an event on their output (left hand) signals, only if one of its input right-hand) signals change b. The INTERNAL assignment statement are only evaluated if the PROCESS block is entered/triggered and the control flow logic inside it executes the assignment statement Signal events produced by assignment statements INSIDE the PROCESS block which are evaluated or executed by the control flow will be placed on scheduled only after we exit the process() block d. Simulated logic TIME will NOT usually change or increase INSIDE a PROCESS block unless explicit time WAIT statements are included in the PROCESS block e. All of the above 8. For an FSM the maximum clock speed (minimum clock period) depends on which factors: a. The time for State FFs to change into the new State after the clock edge b. The time for new State values to propagate through the Next State decoder logic C. The State FFs set-up time for the Next State signals d. The State FFs hold time for the Next State signals. e. Alternatives a,b,c 9. Assign a numerical order from 1 to 10 to the beginning of each tool chain process or design step listed below. This should be the order in which the design steps and design tools of the Vivado Integrated Design Environment (IDE) are carried out by a Hardware designer. (worth 10 points) Create a Test Bench Model for the Digital System b. Create a Constraints file for the given FPGA and the created Digital Design C. Choose the FPGA and/or Development Board Create a Model of the Digital System Simulate the Digital System using the Test Bench Model Elaborate or flatten the hierarchical Digital system design 8. Synthesize the Digital System Usai Bo

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock