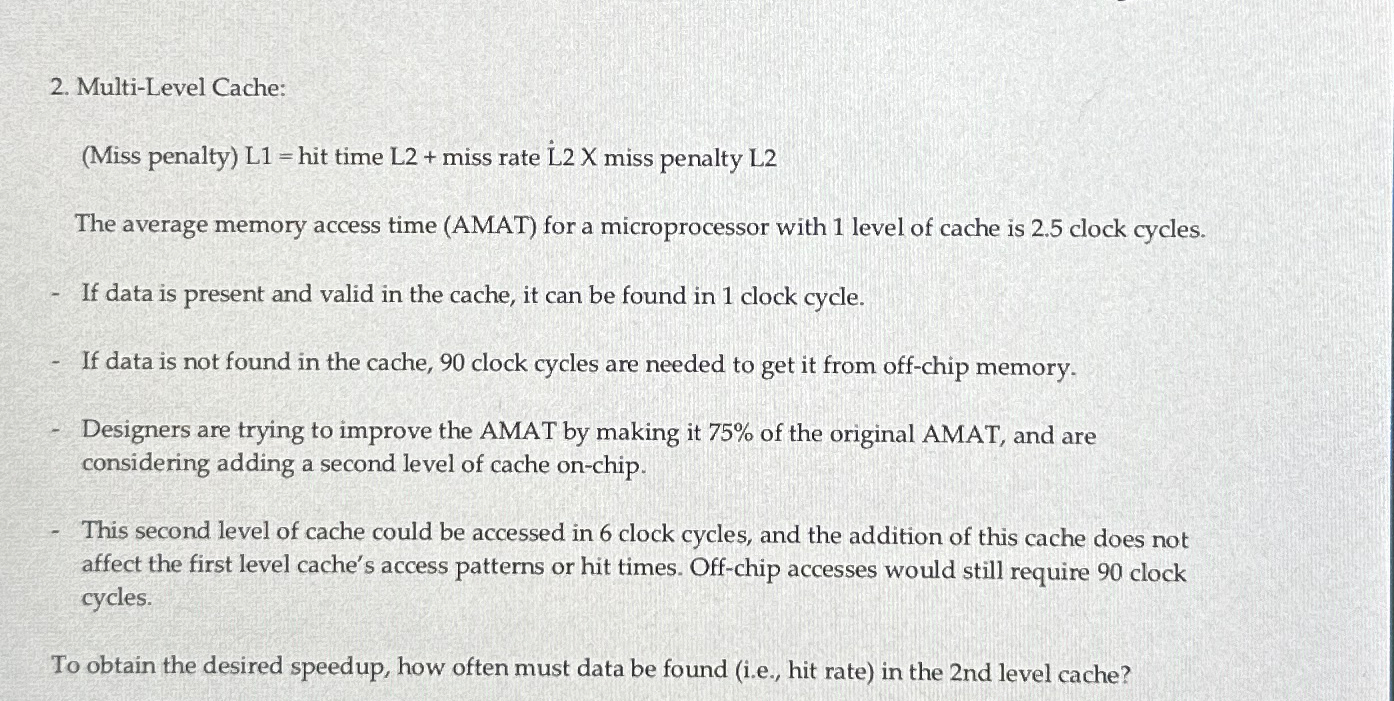

Question: Multi - Level Cache: ( Miss penalty ) L 1 = hit time L 2 + miss rate L 2 x miss penalty L 2

MultiLevel Cache:

Miss penalty hit time miss rate miss penalty

The average memory access time AMAT for a microprocessor with level of cache is clock cycles.

If data is present and valid in the cache, it can be found in clock cycle.

If data is not found in the cache, clock cycles are needed to get it from offchip memory.

Designers are trying to improve the AMAT by making it of the original AMAT, and are considering adding a second level of cache onchip.

This second level of cache could be accessed in clock cycles, and the addition of this cache does not affect the first level cache's access patterns or hit times. Offchip accesses would still require clock cycles.

To obtain the desired speedup, how often must data be found ie hit rate in the nd level cache?

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock