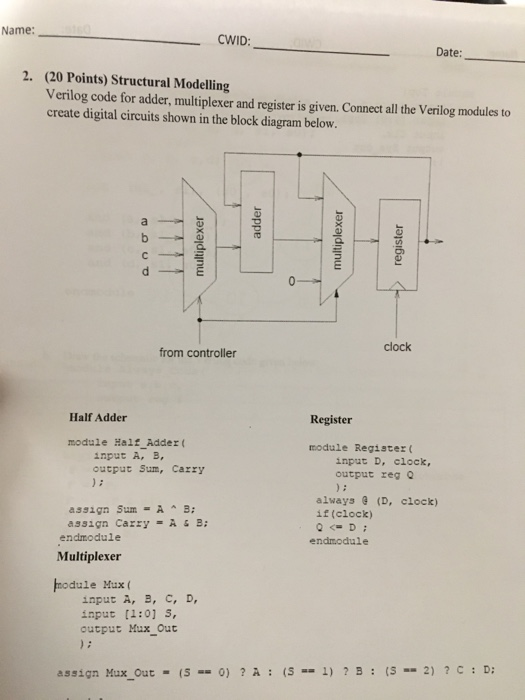

Question: Name: CWID Date:_ 2. (20 Points) Structural Modelling Verilog code for adder, multiplexer and register is given. Connect all the Verilog modules to create digital

Name: CWID Date:_ 2. (20 Points) Structural Modelling Verilog code for adder, multiplexer and register is given. Connect all the Verilog modules to create digital circuits shown in the block diagram below. clock from controller Half Adder Register module Haif Adder( module Register input A, B, output Sum, Cazry input D, clock, output reg o always (D, clock) if (clock) assign Sum A B: assign Carzy A&B endmodule Multiplexer module Mux endnodule input A, B, C, D, inpue [i:01 S, output Mux Out assign Mux Out (s 0) ? A (S1) 2B: (5 2) 2C: D

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts