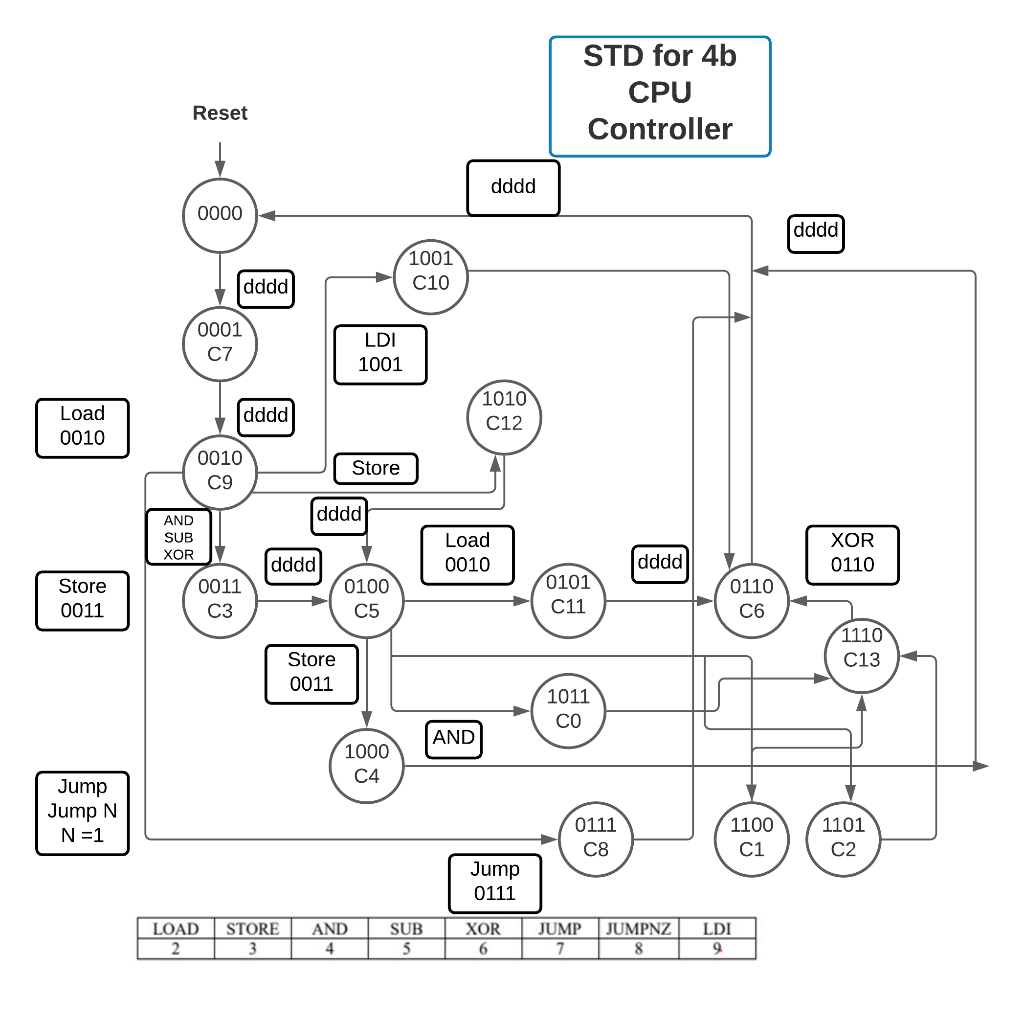

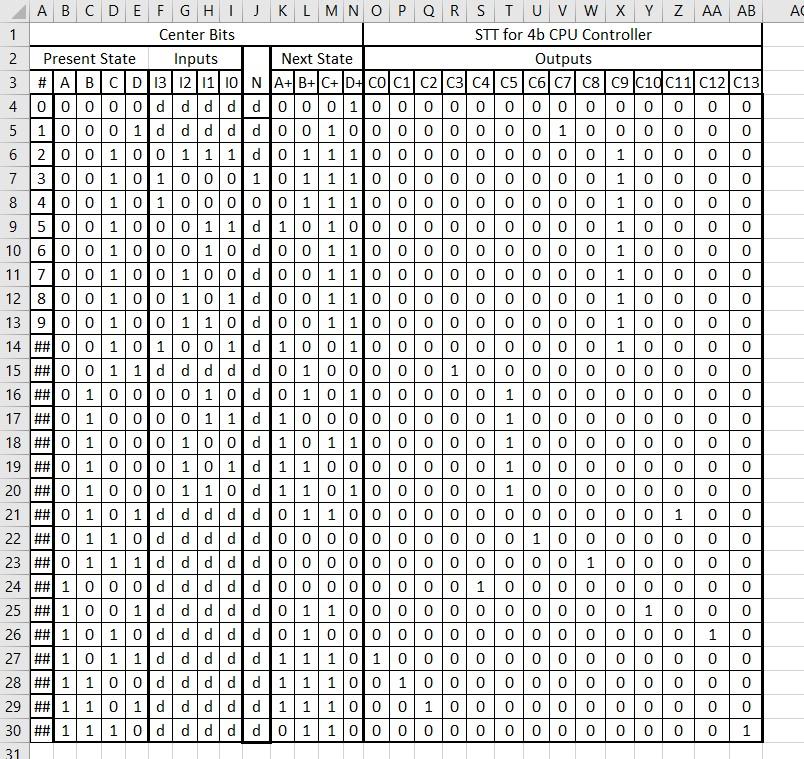

Question: Need help on design a D's flip flop circuit from the STD and STT. STD for 4b CPU Controller Reset dddd 0000 + dddd 1001

Need help on design a D's flip flop circuit from the STD and STT.

STD for 4b CPU Controller Reset dddd 0000 + dddd 1001 C10 dddd 0001 C7 LDI 1001 dddd Load 0010 1010 C12 0010 C9 Store dddd AND SUB XOR Load 0010 XOR 0110 dddd dddd Store 0011 0011 C3 0100 C5 0101 C11 0110 C6 1110 C13 Store 0011 1011 AND 1000 C4 Jump Jump N N=1 0111 C8 1100 C1 1101 C2 Jump 0111 LOAD 2 STORE 3 AND 4 SUB XOR 6 JUMP 7 JUMPNZ 8 LDI 9 5 AC 5 LO OOOOOOO A B C D E F G H I J K L M N O P Q R S T U V W X Y Z AA AB 1 Center Bits STT for 4b CPU Controller 2 Present State Inputs Next State Outputs 3 | |AB | CID | 13 | 12||1|10| N A+B+C+Dl colc1c21c3C4 | C5 | C6 cm C8 | c9c1dc111 C12|C13 | 410|000 | 00d | dddd ||0|0|0|1|0|0|0|0|0|0|0 0 0 0 0 0 0 | 0 5 1 | 0|0|0 | 1 | dldldldld | 0 | 0 | 1 | 0|0|0 | 0|0 | 0|0|0 10000 010 6 2|0|01|0|0|1|11d 0 1 1 1 0 0 0 0 0 0 0 001 0 0 0 | 0 7 3 0 0 1 0 1 0 0 1 0 1 1 1 0 0 0 0 0 0 0 0 0 1 0 0 0 | 0 8 4 0 0 1 0 1 0 0 0 0 0 1 1 1 0 0 0 0 0 0 0 010 1 0 0 0 | 0 9 5 0 0 1 0 0 0 11 d 101000000 010 0 0 1 0 0 0 10 | 60 | 0 1 | 0|0|01|0|| 0|0 | 1 | 10 | 0|0|0|0 | 0|0 | 0 0 1 0 | 0 0 | 0) 11 | 00 0 1 | 00|0|d | 0|0 | 1 | 110 | 0|0|0|0|0 | 0 | 0 0 1 010 0|0 12 18 | 0|0 1 | 000 | 1 0 | 1 | d | 0|0 | 1 | 10 | 0|0|0|0 | 0|0 | 0 0 1 0 | 0 010 13 | 9 10 | 0 | 1 | 0|0 | 1 | 1 | 00d | 0|0 | 1|1|0 | 0 | 0|0 | 0 | 0 | 0 | 0 0 1 010 010 14 ## 0 0 1 0 1 0 0 1 d 1 | 0|0|1|0 | 0 | 0|0|0|0|0 | 0 | 0 1 010 0 | 0 15 11 0 0 0 | 1 | 1 |d | d|d | dd | 0 | 1 | 0 00 0 | 0|0|1|0|0 | 0 | 0 0 0 | 0 010 16 ## 0 1 0 0 0 0 1 0 0 1 0 1 0 0 0 0 0 1 0 0 0 0 010 10 | 0 17 1 0 | 1 | 0|00|0|1|1| | 1 | 0|00|0|0|0|0 | 1 | 0 | 0 0 0 00 10 | 0 18 ## 0 | 1 | 0 | 0000 | 1 | 0|00| 1 0 1 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0 19 ## 0 1 0 0 0 1 0 1 d 1 | 1 | 0||0|0 | 0|0 | 0 | 1 | 0|0|0|0|0|0|0 | 0 20 | 10 | 1 | 0 | 0|0|1| 1 | 0| d||1|0|1|0 | 0|0|0|0|1|0|0|0|0|0|0|0 | 0 21 ||0| 1 | 0 | 1d | dd | dd ||1|1|0|0|0|0|0|0|0|0|0|0|0|0 | 1 | 0 | 0 22 10 | 1 | 1 |0||dldldld 0|0|0||0|00|0|0|0|1|0|0|0|0|0|0|0 23 \10 | 1 | 1 | 1 dldldldldlol00 0|000|0|0|0|0|1|0|0|0 | 0|0 24 | 1 | 0 0 | 00 dldldldldlol000 000|0|1|0|0|0|0|0|0|0|0|0 25 | 1 | 0|0|1||dldldld |0|1|1|00|00|0|0|0|0|0|0|0|1|0|0 | 0 26 1 1 | 01|0||dldldld |0|1|0||0|00|0|0|0|0|0|0|0|0|0 | 1 | 0 27 | ## | 1 | 0|1|1|dldldldld 1 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 28 | 111 | 1 | 0|0 | dd | dldld 1 1 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 29 | ## 1 | 1 |0|1|d | dldldld 1 1 1 0 0 0 1 0 0 00 0 0 0 0 0 0 0 30 |11|1|1|1|00|d | d|d | dld 0 1 1 0 0 0 0 0 0 010 0 0 0 0 0 0 1 31 1 STD for 4b CPU Controller Reset dddd 0000 + dddd 1001 C10 dddd 0001 C7 LDI 1001 dddd Load 0010 1010 C12 0010 C9 Store dddd AND SUB XOR Load 0010 XOR 0110 dddd dddd Store 0011 0011 C3 0100 C5 0101 C11 0110 C6 1110 C13 Store 0011 1011 AND 1000 C4 Jump Jump N N=1 0111 C8 1100 C1 1101 C2 Jump 0111 LOAD 2 STORE 3 AND 4 SUB XOR 6 JUMP 7 JUMPNZ 8 LDI 9 5 AC 5 LO OOOOOOO A B C D E F G H I J K L M N O P Q R S T U V W X Y Z AA AB 1 Center Bits STT for 4b CPU Controller 2 Present State Inputs Next State Outputs 3 | |AB | CID | 13 | 12||1|10| N A+B+C+Dl colc1c21c3C4 | C5 | C6 cm C8 | c9c1dc111 C12|C13 | 410|000 | 00d | dddd ||0|0|0|1|0|0|0|0|0|0|0 0 0 0 0 0 0 | 0 5 1 | 0|0|0 | 1 | dldldldld | 0 | 0 | 1 | 0|0|0 | 0|0 | 0|0|0 10000 010 6 2|0|01|0|0|1|11d 0 1 1 1 0 0 0 0 0 0 0 001 0 0 0 | 0 7 3 0 0 1 0 1 0 0 1 0 1 1 1 0 0 0 0 0 0 0 0 0 1 0 0 0 | 0 8 4 0 0 1 0 1 0 0 0 0 0 1 1 1 0 0 0 0 0 0 0 010 1 0 0 0 | 0 9 5 0 0 1 0 0 0 11 d 101000000 010 0 0 1 0 0 0 10 | 60 | 0 1 | 0|0|01|0|| 0|0 | 1 | 10 | 0|0|0|0 | 0|0 | 0 0 1 0 | 0 0 | 0) 11 | 00 0 1 | 00|0|d | 0|0 | 1 | 110 | 0|0|0|0|0 | 0 | 0 0 1 010 0|0 12 18 | 0|0 1 | 000 | 1 0 | 1 | d | 0|0 | 1 | 10 | 0|0|0|0 | 0|0 | 0 0 1 0 | 0 010 13 | 9 10 | 0 | 1 | 0|0 | 1 | 1 | 00d | 0|0 | 1|1|0 | 0 | 0|0 | 0 | 0 | 0 | 0 0 1 010 010 14 ## 0 0 1 0 1 0 0 1 d 1 | 0|0|1|0 | 0 | 0|0|0|0|0 | 0 | 0 1 010 0 | 0 15 11 0 0 0 | 1 | 1 |d | d|d | dd | 0 | 1 | 0 00 0 | 0|0|1|0|0 | 0 | 0 0 0 | 0 010 16 ## 0 1 0 0 0 0 1 0 0 1 0 1 0 0 0 0 0 1 0 0 0 0 010 10 | 0 17 1 0 | 1 | 0|00|0|1|1| | 1 | 0|00|0|0|0|0 | 1 | 0 | 0 0 0 00 10 | 0 18 ## 0 | 1 | 0 | 0000 | 1 | 0|00| 1 0 1 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0 19 ## 0 1 0 0 0 1 0 1 d 1 | 1 | 0||0|0 | 0|0 | 0 | 1 | 0|0|0|0|0|0|0 | 0 20 | 10 | 1 | 0 | 0|0|1| 1 | 0| d||1|0|1|0 | 0|0|0|0|1|0|0|0|0|0|0|0 | 0 21 ||0| 1 | 0 | 1d | dd | dd ||1|1|0|0|0|0|0|0|0|0|0|0|0|0 | 1 | 0 | 0 22 10 | 1 | 1 |0||dldldld 0|0|0||0|00|0|0|0|1|0|0|0|0|0|0|0 23 \10 | 1 | 1 | 1 dldldldldlol00 0|000|0|0|0|0|1|0|0|0 | 0|0 24 | 1 | 0 0 | 00 dldldldldlol000 000|0|1|0|0|0|0|0|0|0|0|0 25 | 1 | 0|0|1||dldldld |0|1|1|00|00|0|0|0|0|0|0|0|1|0|0 | 0 26 1 1 | 01|0||dldldld |0|1|0||0|00|0|0|0|0|0|0|0|0|0 | 1 | 0 27 | ## | 1 | 0|1|1|dldldldld 1 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 28 | 111 | 1 | 0|0 | dd | dldld 1 1 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 29 | ## 1 | 1 |0|1|d | dldldld 1 1 1 0 0 0 1 0 0 00 0 0 0 0 0 0 0 30 |11|1|1|1|00|d | d|d | dld 0 1 1 0 0 0 0 0 0 010 0 0 0 0 0 0 1 31 1

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts