Question: Need help with writing verilog code that acts like a stop watch, goes up to 5mins and uses 100mhz clock as input which is built

Need help with writing verilog code that acts like a stop watch, goes up to 5mins and uses 100mhz clock as input which is built in the fpga board. Need to include enable and reset in the code.

Need help with writing verilog code that acts like a stop watch, goes up to 5mins and uses 100mhz clock as input which is built in the fpga board. Need to include enable and reset in the code.

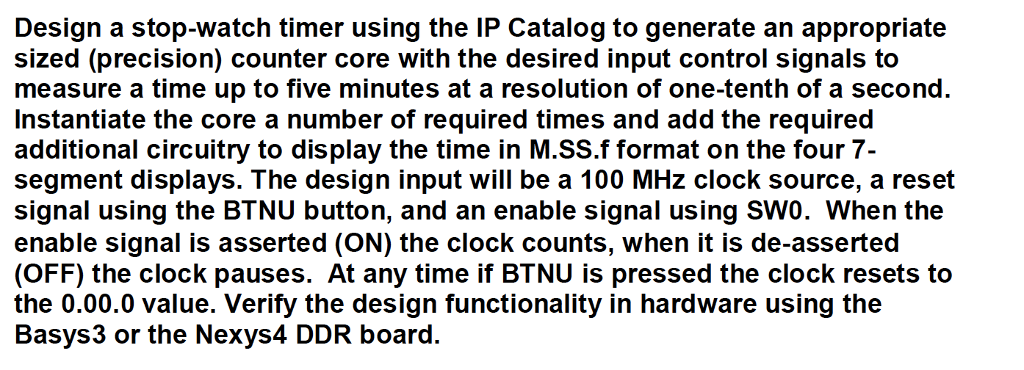

Design a stop-watch timer using the IP Catalog to generate an appropriate sized (precision) counter core with the desired input control signals to measure a time up to five minutes at a resolution of one-tenth of a second. Instantiate the core a number of required times and add the required additional circuitry to display the time in M.SS.f format on the four 7- segment displays. The design input will be a 100 MHz clock source, a reset signal using the BTNU button, and an enable signal using SWO. When the enable signal is asserted (ON) the clock counts, when it is de-asserted (OFF) the clock pauses. At any time if BTNU is pressed the clock resets t

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts