Question: Old MathJax webview Course: computer architecture Problem-3: A. Consider a computer system that has a cache with 512 lines, with each line can store 64

Old MathJax webview

Course: computer architecture Problem-3: A. Consider a computer system that has a cache with 512 lines, with each line can store 64 bytes. Determine the cache line or set the main memory address FAE390H will map to if the cache was: 1. A direct-mapped cache 2. A 4-way set-associative cache 3. An 8-way set-associative cache

B. The L2 data cache of a CPU is a 4KB, 2-Way Set Associative cache with 32-byte lines. The CPU can address 8 MB of main memory.

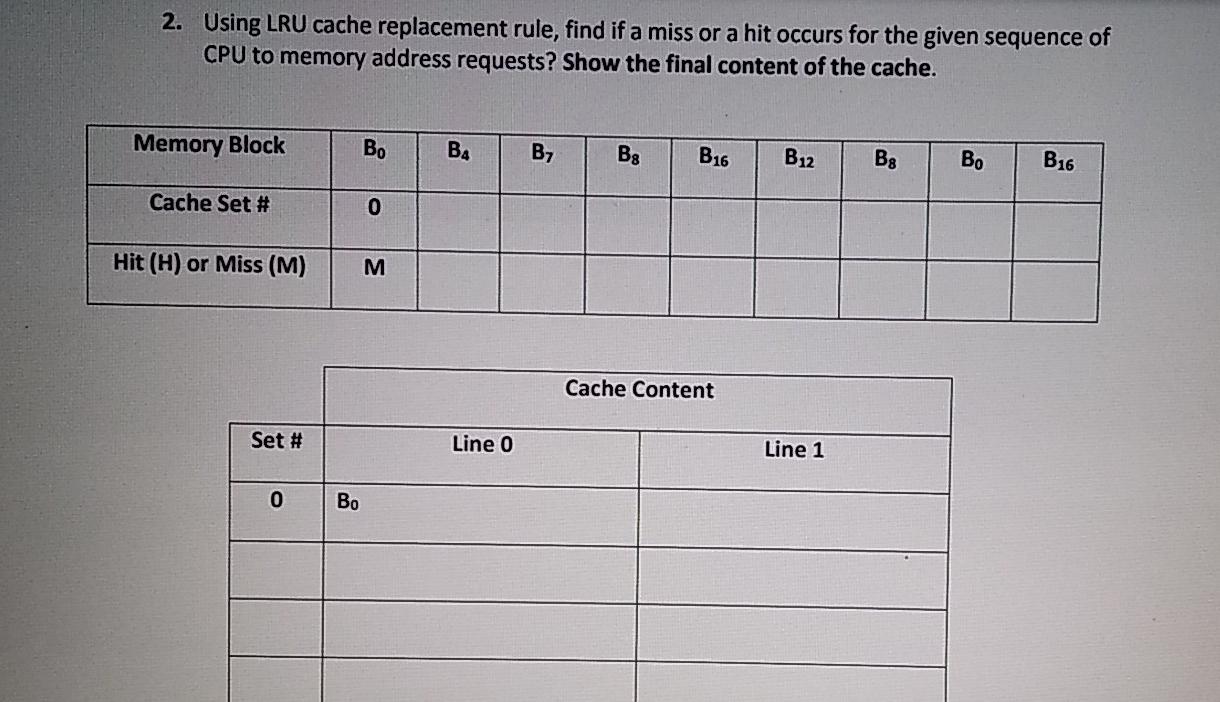

1. What is the address mapping format (number of bits for TAG, SET, and WORD OFFSET). 2. Using LRU cache replacement rule, find if a miss or a hit occurs for the given sequence of CPU to memory address requests? Show the final content of the cache.

What you mean ??? I want to solve this question quickly, I don't want to lose this attempt?????.!!!

2. Using LRU cache replacement rule, find if a miss or a hit occurs for the given sequence of CPU to memory address requests? Show the final content of the cache. Memory Block BA B Ba B16 B12 Bg BO B16 Cache Set # 0 Hit (H) or Miss (M) M Cache Content Set # Line 0 Line 1 0

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts