Question: P1 (10 points): Using the expression for 2-1 multiplexers and 4-1 multiplexers, show that the expression for T in the following circuit is T=(W+X)(Y +

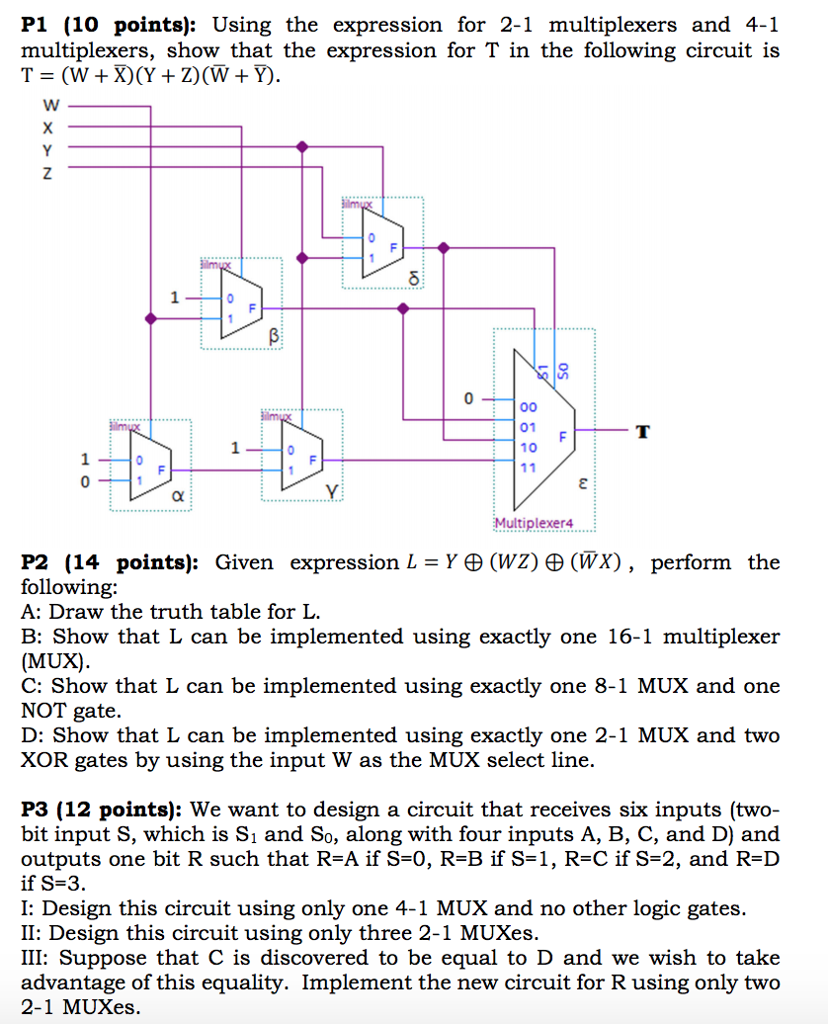

P1 (10 points): Using the expression for 2-1 multiplexers and 4-1 multiplexers, show that the expression for T in the following circuit is T=(W+X)(Y + Z)(W+T) 01 10 Multiplexer P2 (14 points): Given expression l=Y(WZ)(WX), perform the following: A: Draw the truth table for L B: Show that L can be implemented using exactly one 16-1 multiplexer (MUX) C: Show that L can be implemented using exactly one 8-1 MUX and one NOT gate. D: Show that L can be implemented using exactly one 2-1 MUX and two XOR gates by using the input W as the MUX select line. P3 (12 points): We want to design a circuit that receives six inputs (two- bit input S, which is S and So, along with four inputs A, B, C, and D) and outputs one bit R such that R-A if S-0, R-B if S-1, R-C if S-2, and R-D if S-3. I: Design this circuit using only one 4-1 MUX and no other logic gates. II: Design this circuit using only three 2-1 MUXes. III: Suppose that C is discovered to be equal to D and we wish to take advantage of this equality. Implement the new circuit for R using only two 2-1 MUXes. P1 (10 points): Using the expression for 2-1 multiplexers and 4-1 multiplexers, show that the expression for T in the following circuit is T=(W+X)(Y + Z)(W+T) 01 10 Multiplexer P2 (14 points): Given expression l=Y(WZ)(WX), perform the following: A: Draw the truth table for L B: Show that L can be implemented using exactly one 16-1 multiplexer (MUX) C: Show that L can be implemented using exactly one 8-1 MUX and one NOT gate. D: Show that L can be implemented using exactly one 2-1 MUX and two XOR gates by using the input W as the MUX select line. P3 (12 points): We want to design a circuit that receives six inputs (two- bit input S, which is S and So, along with four inputs A, B, C, and D) and outputs one bit R such that R-A if S-0, R-B if S-1, R-C if S-2, and R-D if S-3. I: Design this circuit using only one 4-1 MUX and no other logic gates. II: Design this circuit using only three 2-1 MUXes. III: Suppose that C is discovered to be equal to D and we wish to take advantage of this equality. Implement the new circuit for R using only two 2-1 MUXes

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts