Question: Pipeline Execution and Performance Task: Consider the following ARM code: Start AND RO,R1, #0 OR R1,R0, #40 LDRB R2, [R1,RO] LDRB R3, RI, #21 ADD

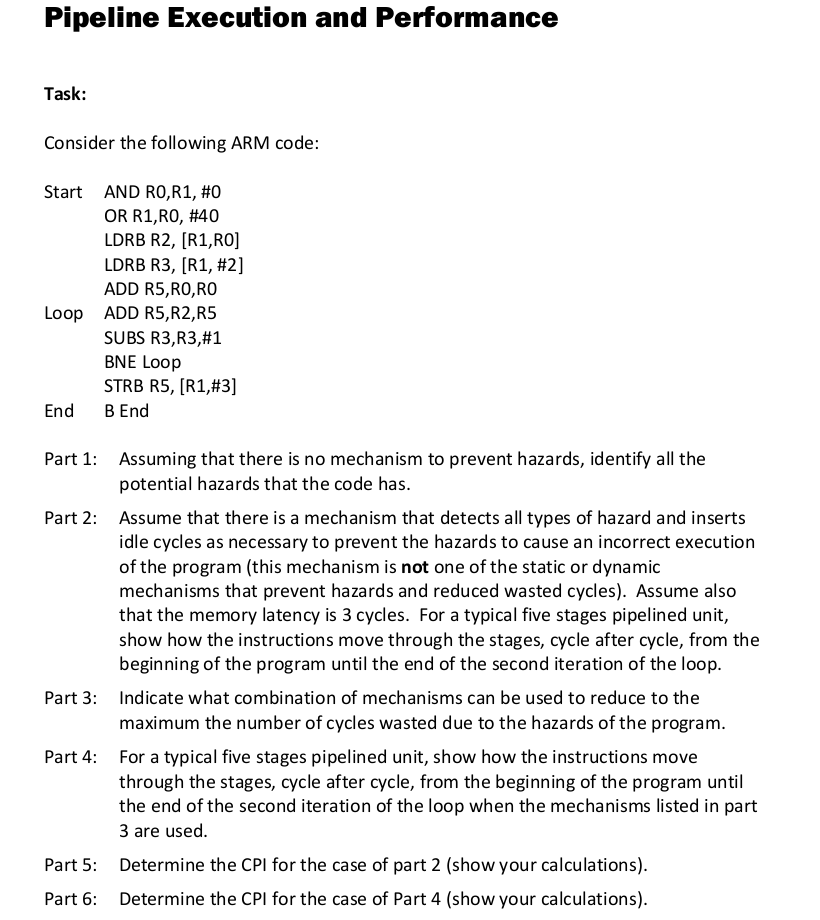

Pipeline Execution and Performance Task: Consider the following ARM code: Start AND RO,R1, #0 OR R1,R0, #40 LDRB R2, [R1,RO] LDRB R3, RI, #21 ADD R5,RO,RO Loop ADD R5,R2,R5 SUBS R3,R3,#1 BNE Loop STRB R5, RI,#31 End B End Part 1: Assuming that there is no mechanism to prevent hazards, identify all the Part 2: Assume that there is a mechanism that detects all types of hazard and inserts potential hazards that the code has idle cycles as necessary to prevent the hazards to cause an incorrect execution of the program (this mechanism is not one of the static or dynamic mechanisms that prevent hazards and reduced wasted cycles). Assume also that the memory latency is 3 cycles. For a typical five stages pipelined unit, show how the instructions move through the stages, cycle after cycle, from the beginning of the program until the end of the second iteration of the loop Indicate what combination of mechanisms can be used to reduce to the maximum the number of cycles wasted due to the hazards of the program For a typical five stages pipelined unit, show how the instructions move through the stages, cycle after cycle, from the beginning of the program until the end of the second iteration of the loop when the mechanisms listed in part 3 are used Part 3: Part 4: Part 5: Determine the CPI for the case of part 2 (show your calculations) Determine the CPI for the case of Part 4 (show your calculations) Part 6

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts