Question: PLEASE ANSWER ALL PARTS AND SHOW WORK PROCESS FOR EACH PART Suppose I am designing a microprocessor based system. It has 5 components on it.

PLEASE ANSWER ALL PARTS AND SHOW WORK PROCESS FOR EACH PART

PLEASE ANSWER ALL PARTS AND SHOW WORK PROCESS FOR EACH PART

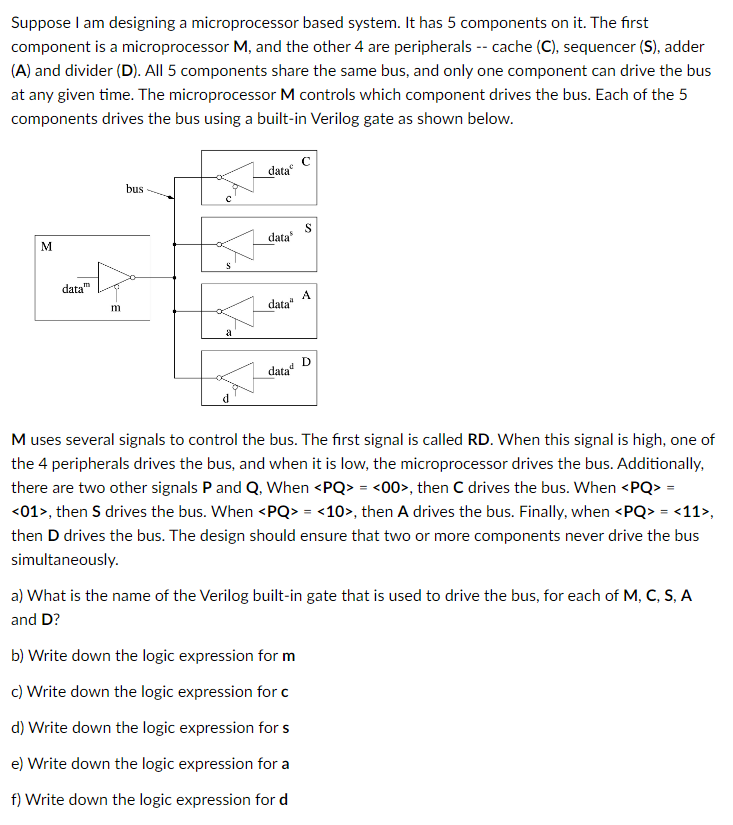

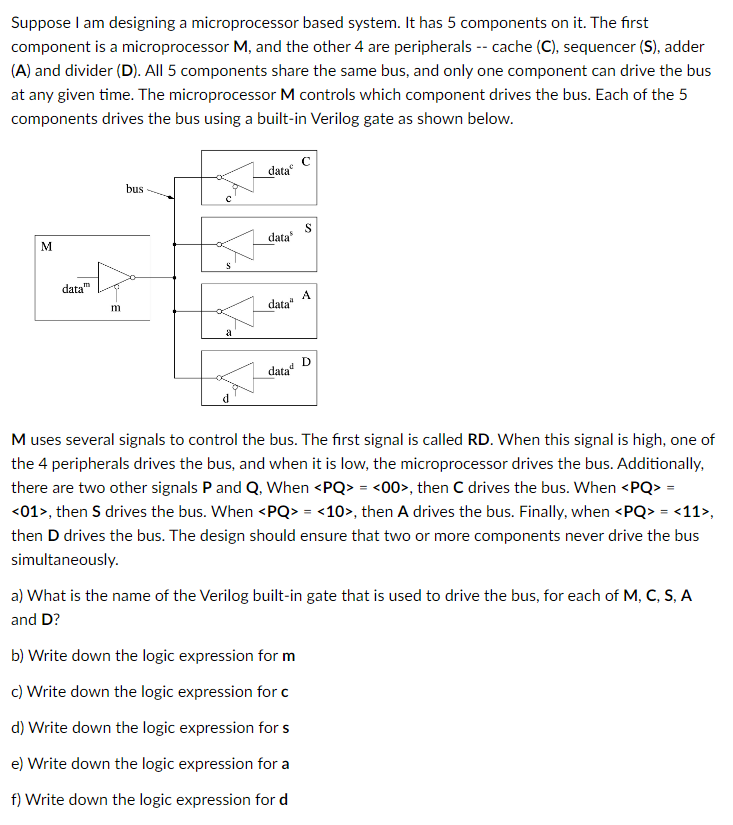

Suppose I am designing a microprocessor based system. It has 5 components on it. The first component is a microprocessor M, and the other 4 are peripherals -- cache (C), sequencer (S), adder (A) and divider (D). All 5 components share the same bus, and only one component can drive the bus at any given time. The microprocessor M controls which component drives the bus. Each of the 5 components drives the bus using a built-in Verilog gate as shown below. data bus S data M S m data m data" a D data d Muses several signals to control the bus. The first signal is called RD. When this signal is high, one of the 4 peripherals drives the bus, and when it is low, the microprocessor drives the bus. Additionally, there are two other signals P and Q, When = , then C drives the bus. When = , then S drives the bus. When = = , then D drives the bus. The design should ensure that two or more components never drive the bus simultaneously. a) What is the name of the Verilog built-in gate that is used to drive the bus, for each of M, C, S, A and D? b) Write down the logic expression form c) Write down the logic expression for c d) Write down the logic expression for s e) Write down the logic expression for a f) Write down the logic expression for d Suppose I am designing a microprocessor based system. It has 5 components on it. The first component is a microprocessor M, and the other 4 are peripherals -- cache (C), sequencer (S), adder (A) and divider (D). All 5 components share the same bus, and only one component can drive the bus at any given time. The microprocessor M controls which component drives the bus. Each of the 5 components drives the bus using a built-in Verilog gate as shown below. data bus S data M S m data m data" a D data d Muses several signals to control the bus. The first signal is called RD. When this signal is high, one of the 4 peripherals drives the bus, and when it is low, the microprocessor drives the bus. Additionally, there are two other signals P and Q, When = , then C drives the bus. When = , then S drives the bus. When = = , then D drives the bus. The design should ensure that two or more components never drive the bus simultaneously. a) What is the name of the Verilog built-in gate that is used to drive the bus, for each of M, C, S, A and D? b) Write down the logic expression form c) Write down the logic expression for c d) Write down the logic expression for s e) Write down the logic expression for a f) Write down the logic expression for d

PLEASE ANSWER ALL PARTS AND SHOW WORK PROCESS FOR EACH PART

PLEASE ANSWER ALL PARTS AND SHOW WORK PROCESS FOR EACH PART