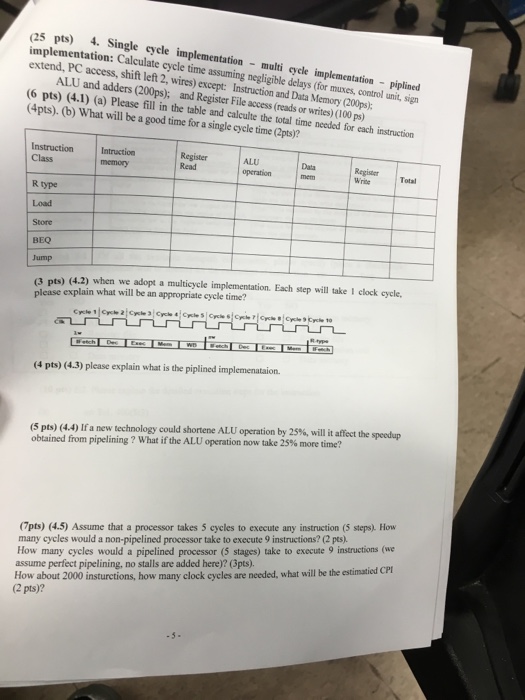

Question: please answer and show all work (25 Single implementation: Calculate cycle time cycle i cycle ALU access, shift left wires) assuming negligible delays entation (6

please answer and show all work

please answer and show all work (25 Single implementation: Calculate cycle time cycle i cycle ALU access, shift left wires) assuming negligible delays entation (6 and adders 2, except: (for muxes, control unit, sign pts) (4.1) (200ps); and Register Instruction and Data (4pts). (a) Please fill in File access (reads or writ 100 ps) (b) What will the table and the total time needed for each instruction be a good time for a single cycle time (2pts)? Instruction Intruction pts) (4.2) when we a multicycle implementation. Each step will take clock cycle. please explain what will be an appropriate 4 pts) 4.3 please explain what is the piplined implemenataion. (5 pts) a new technology could shortene U operation by it affect the speedup obtained from 25%, will pipelining What if the ALU operation now take 25% more time? Cpts) (4.50 Assume that a processor takes 5 cycles to execute any instruction (5 steps) How many cycles would a non-pipelined processor take to execute 9 instructions? (2 pes). How many cycles would a pipelined processor (5 stages) take to execute 9 instructions (we How about 2000 insturctions, how many clock cycles are needed, what will be the estimatiedcPI pts)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts