Question: Please answer question 3. Question 3 Not yet answered Marked out of 1.00 p Flag question Consider the four-bit prime (or one) number function you

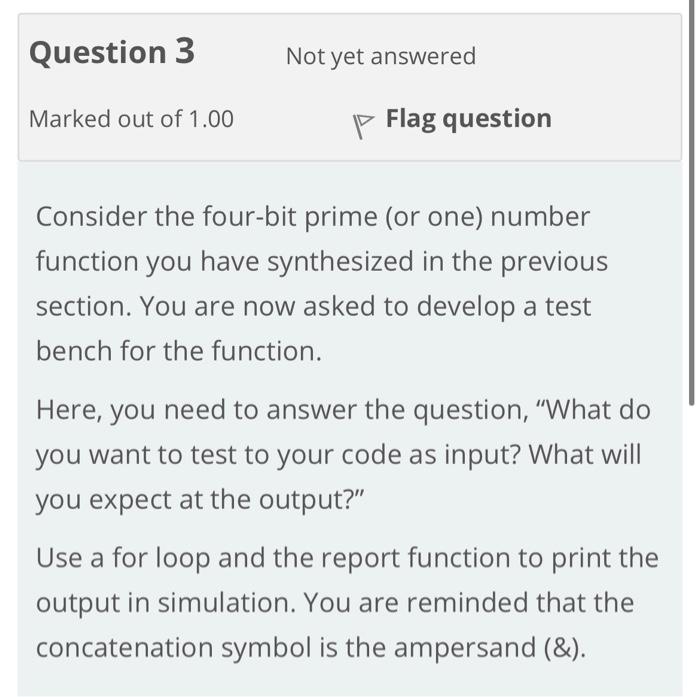

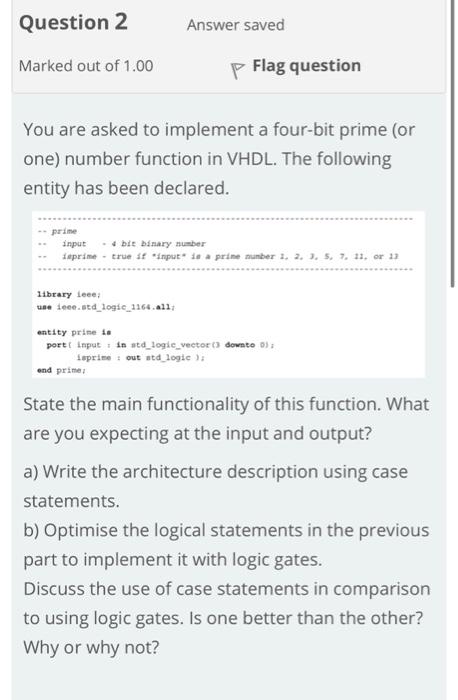

Question 3 Not yet answered Marked out of 1.00 p Flag question Consider the four-bit prime (or one) number function you have synthesized in the previous section. You are now asked to develop a test bench for the function. Here, you need to answer the question, "What do you want to test to your code as input? What will you expect at the output?" Use a for loop and the report function to print the output in simulation. You are reminded that the concatenation symbol is the ampersand (&). Question 2 Answer saved Marked out of 1.00 P Flag question You are asked to implement a four-bit prime (or one) number function in VHDL. The following entity has been declared. - prime input-4bit binary number ieprime true sf input 1e a prime number 3, 2. 3. 5. 7. 21. or 13 library Lee une dece.std_logic_1164.all entity prime is portt input in atd_logic_vector) downto); ieprime out atd logic; and prime State the main functionality of this function. What are you expecting at the input and output? a) Write the architecture description using case statements. b) Optimise the logical statements in the previous part to implement it with logic gates. Discuss the use of case statements in comparison to using logic gates. Is one better than the other? Why or why not

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts