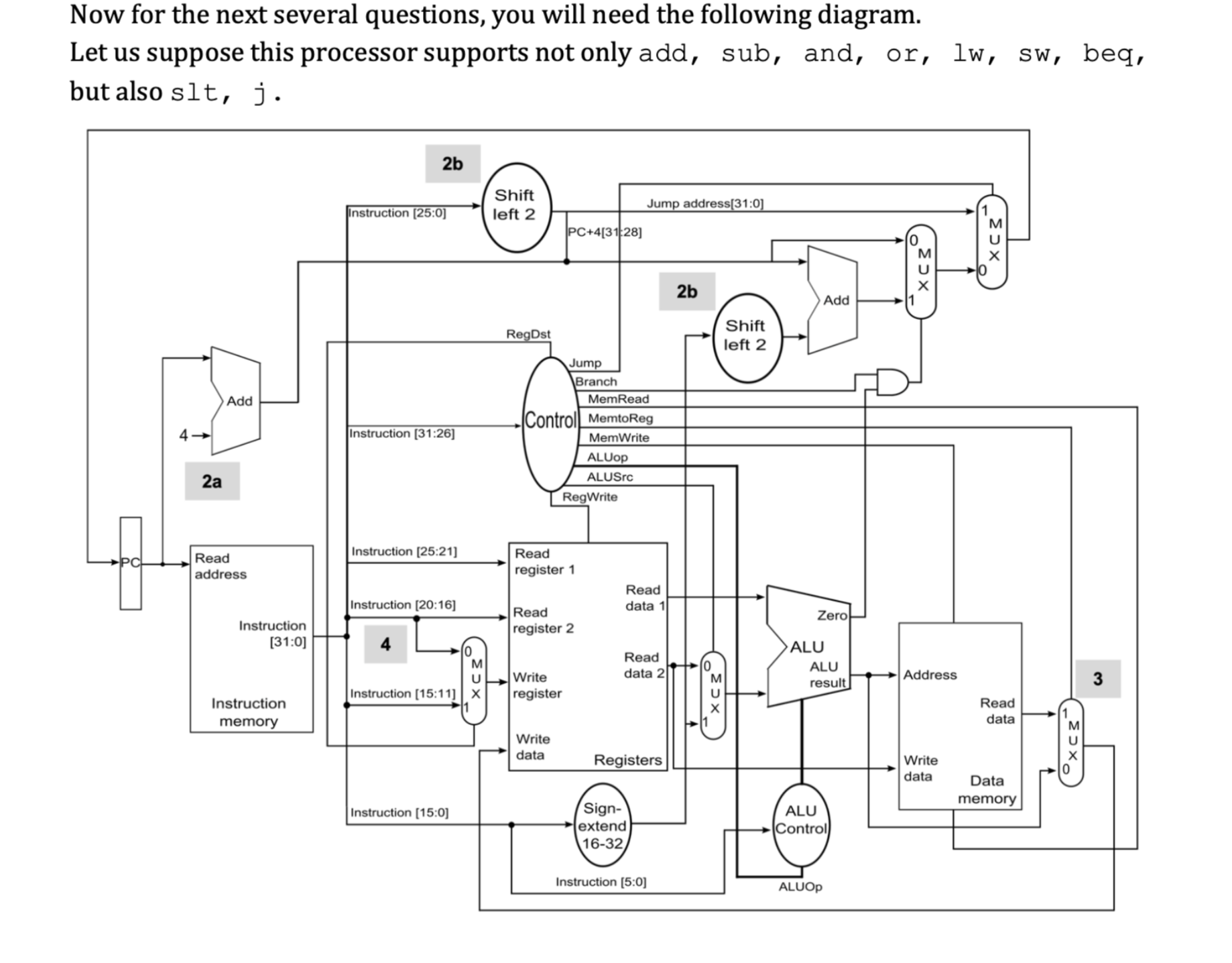

Question: Please answer the questions below: 5 . How do beq and j differ, and can you briefly explain how each one is executed in this

Please answer the questions below:

How do beq and j differ, and can you briefly explain how each one is executed in this circuit? Explain the significance of b the shift left

Hint: Note that there are now two of them, the lower one is familiar and is needed for beq while the upper one is needed for j What are they doing? Why do we do this shiftleft ie multiply by Its something needed in both cases

Let us suppose the MemToReg control line is defective and gets stuck at Which of the supported instructions will always execute correctly? And which ones can possibly execute correctly, and under what circumstances?

By execute correctly we mean produce the correct results, AND do not produce unintended side effects The processor without a defective control line is the standard for determining correct results and side effects.

Look at Instruction: under the instruction lw These bits specify the target Write register. The control signal RegDst is set to for this purpose. However, these bits are also fed into Read Register So the output bus Read Data is set with whatever junk value was in the register already. Explain why this unintended read register is not a problem.

Hint: we stop this getting into the ALU, and we dont set the memory to be ready for a write.

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock