Question: Please Design a 64-bit carry-lookahead adder using 4 16-bit carry-lookahead adders. Derive the equations specified in part a, and answer the questions in parts b

Please Design a 64-bit carry-lookahead adder using 4 16-bit carry-lookahead adders. Derive the equations specified in part a, and answer the questions in parts b and c please!

The textbook reference is Computer Organization and Embedded Systems (Authors: Hamacher, Vranesic, Zaky, and Manjikian) 6th edition.

Will rate promptly if the answer is correct!

Thanks for help

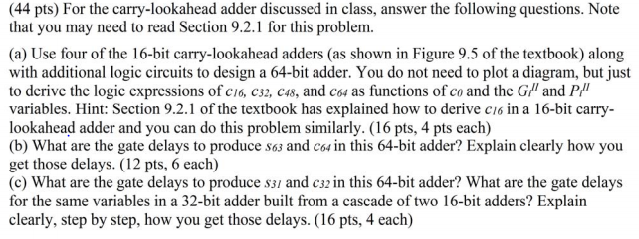

44 pts) For the carry-lookahead adder discussed in class, answer the following questions. Note that you may need to read Section 9.2.1 for this problem. (a) Use four of the 16-bit carry-lookahead adders (as shown in Figure 9.5 of the textbook) along with additional logic circuits to design a 64-bit adder. You do not need to plot a diagram, but just to derive thc logic expressions of ci6, C32, c48, and cos as functions of co and the G and P" variables. Hint: Section 9.2.1 of the textbook has explained how to derive ci6 in a 16-bit carry- lookahead adder and you can do this problem similarly. (16 pts, 4 pts each) (b) What are the gate delays to produce sos and cos in this 64-bit adder? Explain clearly how you get those delays. (12 pts, 6 each) (c) What are the gate delays to produce si and c32 in this 64-bit adder? What are the gate delays for the same variables in a 32-bit adder built from a cascade of two 16-bit adders? Explain clearly, step by step, how you get those delays. (16 pts, 4 each) 44 pts) For the carry-lookahead adder discussed in class, answer the following questions. Note that you may need to read Section 9.2.1 for this problem. (a) Use four of the 16-bit carry-lookahead adders (as shown in Figure 9.5 of the textbook) along with additional logic circuits to design a 64-bit adder. You do not need to plot a diagram, but just to derive thc logic expressions of ci6, C32, c48, and cos as functions of co and the G and P" variables. Hint: Section 9.2.1 of the textbook has explained how to derive ci6 in a 16-bit carry- lookahead adder and you can do this problem similarly. (16 pts, 4 pts each) (b) What are the gate delays to produce sos and cos in this 64-bit adder? Explain clearly how you get those delays. (12 pts, 6 each) (c) What are the gate delays to produce si and c32 in this 64-bit adder? What are the gate delays for the same variables in a 32-bit adder built from a cascade of two 16-bit adders? Explain clearly, step by step, how you get those delays. (16 pts, 4 each)

Step by Step Solution

There are 3 Steps involved in it

Thank you for your patience I will now attempt to process the imag... View full answer

Get step-by-step solutions from verified subject matter experts