Question: Please explain step-by-step how to solve this (a) Suppose you have a 4-way set associative cache with a block size of 32 bytes and a

Please explain step-by-step how to solve this

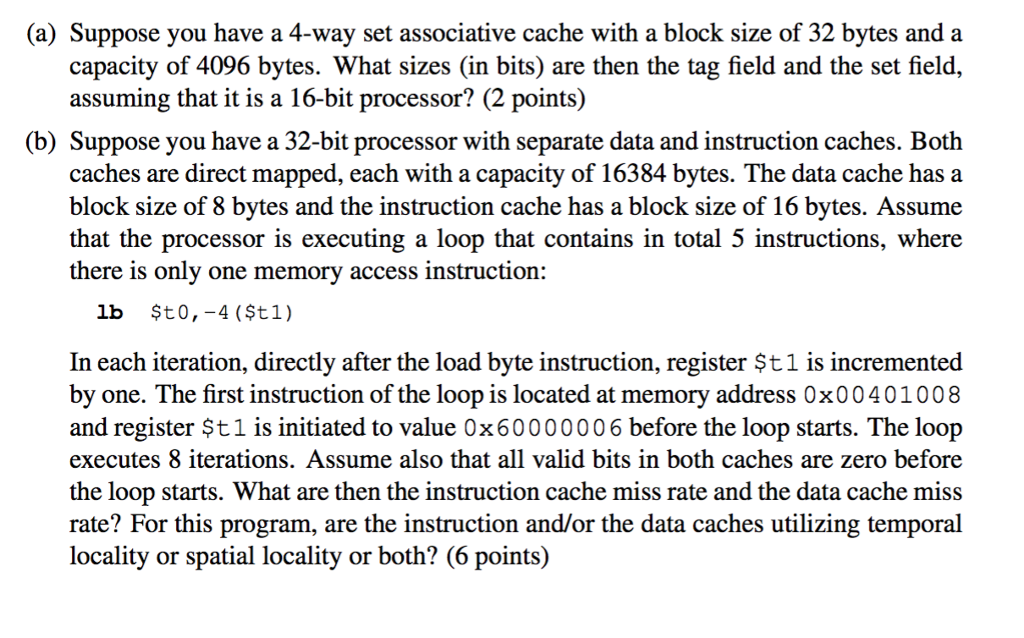

(a) Suppose you have a 4-way set associative cache with a block size of 32 bytes and a capacity of 4096 bytes. What sizes (in bits) are then the tag field and the set fielod, assuming that it is a 16-bit processor? (2 points) (b) Suppose you have a 32-bit processor with separate data and instruction caches. Both caches are direct mapped, each with a capacity of 16384 bytes. The data cache has a block size of 8 bytes and the instruction cache has a block size of 16 bytes. Assume that the processor is executing a loop that contains in total 5 instructions, where there is only one memory access instruction: lb $t0,-4 ($t1) In each iteration, directly after the load byte instruction, register $t1 is incremented by one. The first instruction of the loop is located at memory address 0x00401008 and register $t1 is initiated to value 0x60000006 before the loop starts. The loop executes 8 iterations. Assume also that all valid bits in both caches are zero before the loop starts. What are then the instruction cache miss rate and the data cache miss rate? For this program, are the instruction and/or the data caches utilizing temporal locality or spatial locality or both? (6 points)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts