Question: Please explain the logic of the solution and how it came to be. Problem 2: For each of the following RISC-V program segments described below,

Please explain the logic of the solution and how it came to be.

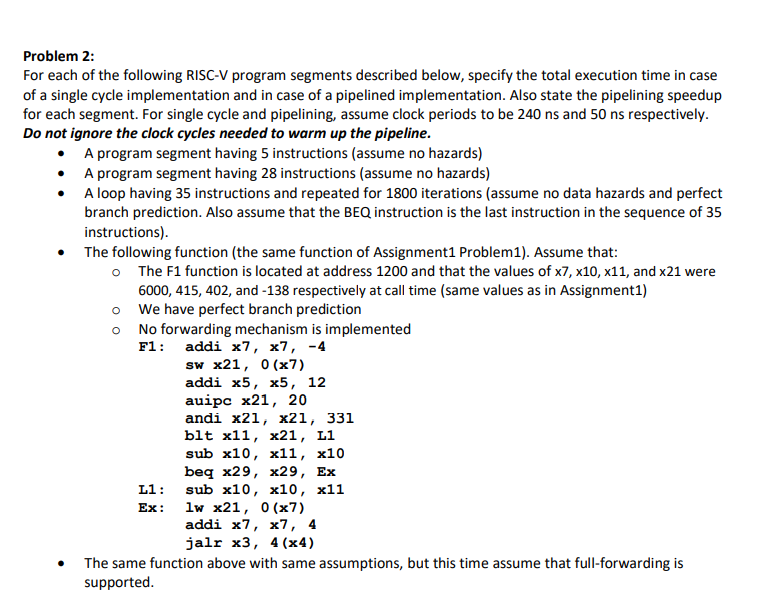

Problem 2: For each of the following RISC-V program segments described below, specify the total execution time in case of a single cycle implementation and in case of a pipelined implementation. Also state the pipelining speedup for each segment. For single cycle and pipelining, assume clock periods to be 240 ns and 50 ns respectively. Do not ignore the clock cycles needed to warm up the pipeline. A program segment having 5 instructions (assume no hazards) A program segment having 28 instructions (assume no hazards) A loop having 35 instructions and repeated for 1800 iterations (assume no data hazards and perfect branch prediction. Also assume that the BEQ instruction is the last instruction in the sequence of 35 instructions). The following function (the same function of Assignment1 Problem1). Assume that: o The F1 function is located at address 1200 and that the values of x7, x10, x11, and x21 were 6000, 415, 402, and -138 respectively at call time (same values as in Assignment1) o We have perfect branch prediction o No forwarding mechanism is implemented F1: addi x7, x7, -4 sw x21, 0 (x7) addi x5, x5, 12 auipc x21, 20 andi x21, x21, 331 blt x11, x21, L1 sub x10, x11, x10 beq x29, x29, Ex L1: sub x10, x10, x11 Ex: lw x21, 0(x7) addi x7, x7, 4 jalr x3, 4(x4) The same function above with same assumptions, but this time assume that full-forwarding is supported

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts