Question: Please get me the right answer; I will rate by the moderator. Thank you for your time and efforts in advance. Use the following architecture

Please get me the right answer; I will rate by the moderator. Thank you for your time and efforts in advance.

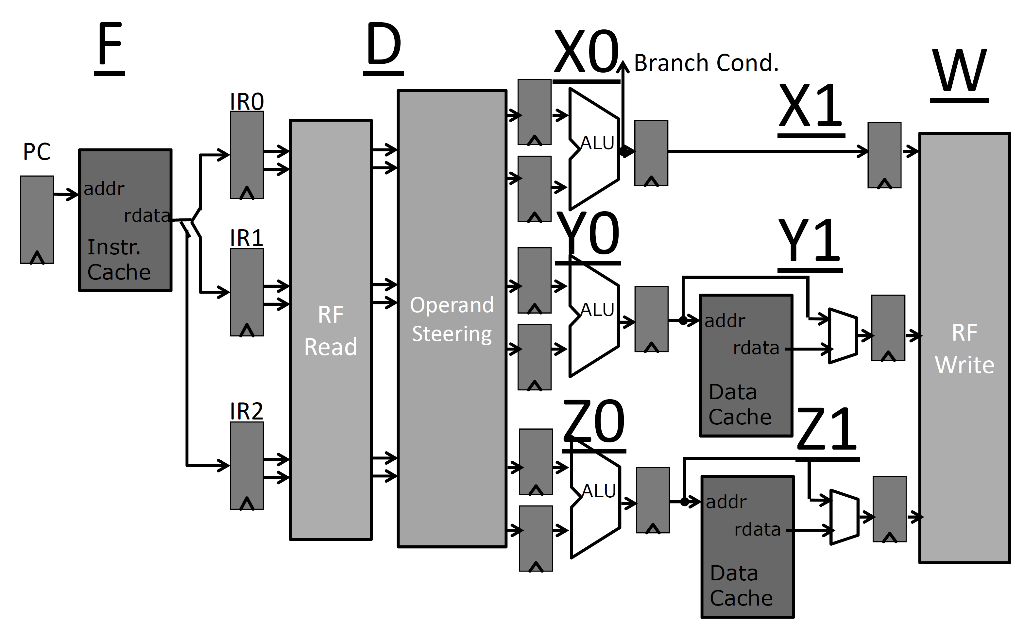

Use the following architecture for questions 6-9:

Given a 3-wide in-order processor, draw the optimal pipeline diagram and answer question 6-9, showing for each instruction, what stage of the pipeline it is in for each cycle for the execution of the code sequence below. Assume full bypassing of values from the respective instruction completion stage to the Decode stage. Assume that pipeline X can execute branches and ALU operations, pipeline Y can excute loads, stores, and ALU operations, and pipeline Z can execute loads, stores, and ALU operations. Loads have a latency of two cycles and ALU operations have a latency of one cycle. Branches are resolved in X0 and the machine has no branch delay slots and always predicts the fallthrough path. The machine can fetch three instructions per cycle, decode three instructions per cycle, execute three instructions per cycle, and writeback three instructions per cycle but maintains data dependencies. The operand steering logic can steer any operand to any ALU to enable any instruction to reach any pipeline, but the pipelines have restrictions on what instructions each can execute as described above. Assume that there are no alignment restrictions on instructions which can be simultaneously fetched from the instruction memory. Also, assume that instructions stall in the decode stage if there are structural or data hazards and stalling one pipeline does not inhibit the fetching of future instructions. The figure below shows the pipeline with pipeline stage names underlined.

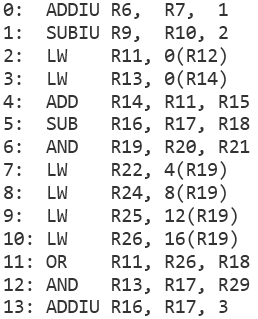

Code sequence for questions 6-9:

Q6 ) Which instructions stall due to data hazard? Check all that apply

a) 4: ADD R14, R11, R15

b) 7: LW R22, 4(R19)

c) 8: LW R24, 8(R19)

d) 10: LW R26, 16(R19)

e) 11: OR R11, R26, R18

f) 13: ADDIU R16, R17, 3

7.Question 7

Which instructions stall due to structural hazard? Select all that apply

a) 4: ADD R14, R11, R15

b) 7: LW R22, 4(R19)

c) 9: LW R25, 12(R19)

d) 11: OR R11, R26, R18

e) 12: AND R13, R17, R29

Q8

Which instructions stall in the fetch stage? Select all that apply

a) 6: AND R19, R20, R21

b) 7: LW R22, 4(R19

c) 11: OR R11, R26, R18

d) 12: AND R13, R17, R29

e) 13: ADDIU R16, R17, 3

Q9

Which instructions stall in the decode stage? Select all that apply

a) 4: ADD R14, R11, R15

b) 6: AND R19, R20, R21

c) 7: LW R22, 4(R19)

d) 9: LW R25, 12(R19)

e) 10: LW R26, 16(R19)

f) 11: OR R11, R26, R18

F XO, Branch Cond. X1 IRO ALU PC addr YO rdata Y1 IR1 Instr. Cache Operand ALU RF addr rdata - RF Steering Read Write Data Cache IR2 Z1 ALU addr rdata Data Cache e: ADDIU R6, R7, 1 SUBIU R9, R10, 2 R11, e(R12) R13, 0(R14) R14, R11, R15 R16, R17, R18 R19, R20, R21 R22, 4(R19) R24, 8(R19) R25, 12(R19) R26, 16(R19) R11, R26, R18 R13, R17, R29 13: ADDIU R16, R17, 3 1: 2: LW 3: LW 4: ADD 5: SUB 6: AND 7: LW 8: LW 9: LW 10: LW 11: OR 12: AND

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts