Question: please help Auser presses and holds down a button x If the user holds down the button for 256 clock cycles (0.25s), the output is

please help

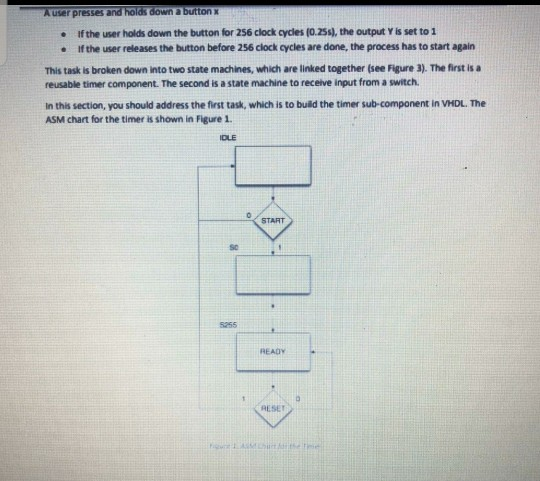

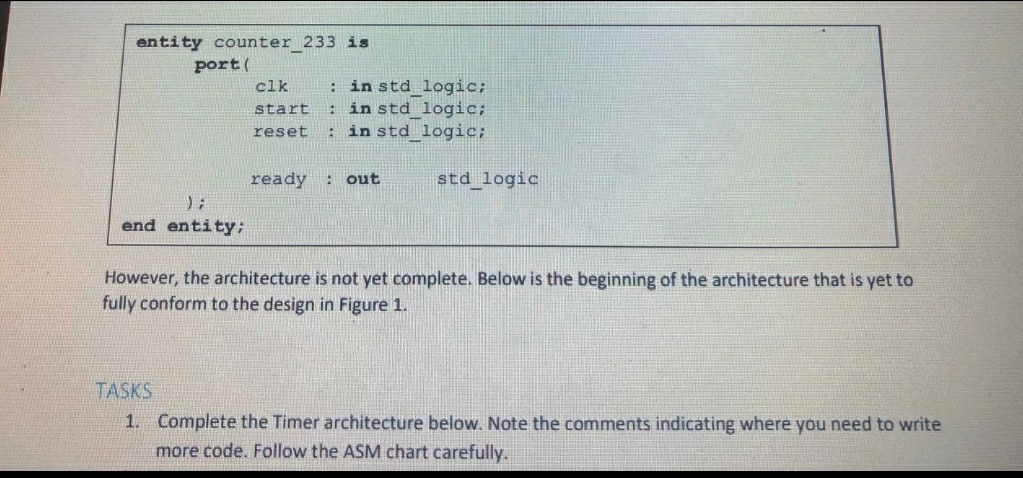

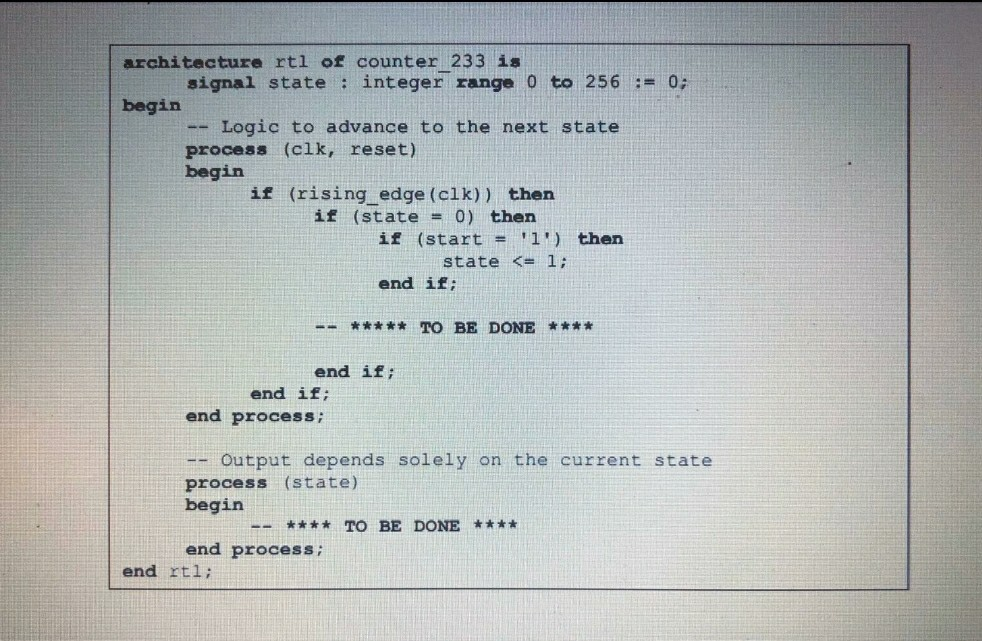

Auser presses and holds down a button x If the user holds down the button for 256 clock cycles (0.25s), the output is set to 1 If the user releases the button before 256 clock cycles are done, the process has to start again This task is broken down into two state machines, which are linked together (see Figure 3). The first is a reusable timer component. The second is a state machine to receive input from a switch In this section, you should address the first task, which is to build the timer sub-component in VHDL. The ASM chart for the timer is shown in Figure 1. START entity counter_233 is port clk : in std_logic; start : in std_logic; reset : in std logic; ready out std_logic end entity; However, the architecture is not yet complete. Below is the beginning of the architecture that is yet to fully conform to the design in Figure 1. TASKS 1. Complete the Timer architecture below. Note the comments indicating where you need to write more code. Follow the ASM chart carefully. architecture rtl of counter_233 is signal state : integer range 0 to 256 := 0; begin -- Logic to advance to the next state process (clk, reset) begin if (rising edge (clk)) then if (state = 0) then if (start = '1') then state

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts