Question: Please help with b) Write a finite state machine (FSM) for an automatic reversible 6 modulo counter as follows: The counter counts 0, 1, 2,

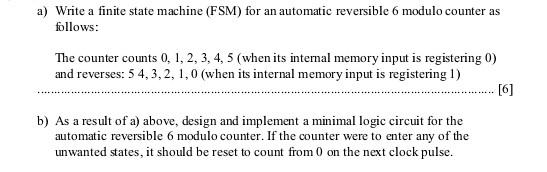

Please help with b) Write a finite state machine (FSM) for an automatic reversible 6 modulo counter as follows: The counter counts 0, 1, 2, 3, 4, 5 (when its internal memory input is registering 0) and reverses: 5 4, 3, 2, 1, 0 (when its internal memory input is registering 1) ......................................................................................................................................... [6] b) As a result of a) above, design and implement a minimal logic circuit for the automatic reversible 6 modulo counter. If the counter were to enter any of the unwanted states, it should be reset to count from 0 on the next clock pulse.

a) Write a finite state machine (FSM) for an automatic reversible 6 modulo counter as follows: The counter counts 0,1,2,3,4,5 (when its internal memory input is registering 0 ) and reverses: 54,3,2,1,0 (when its internal memory input is registering 1) b) As a result of a) above, design and implement a minimal logic circuit for the automatic reversible 6 modulo counter. If the counter were to enter any of the unwanted states, it should be reset to count from 0 on the next clock pulse

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts