Question: Please include test bench and wave simulation Carry-Select Adder (CSA8) diagram: a[7:41 b17:4) a(3:0) b[3:00 cout RCA4 cin0 sum[3:01 sa 17:41 dok cout y MUX

Please include test bench and wave simulation

Please include test bench and wave simulation

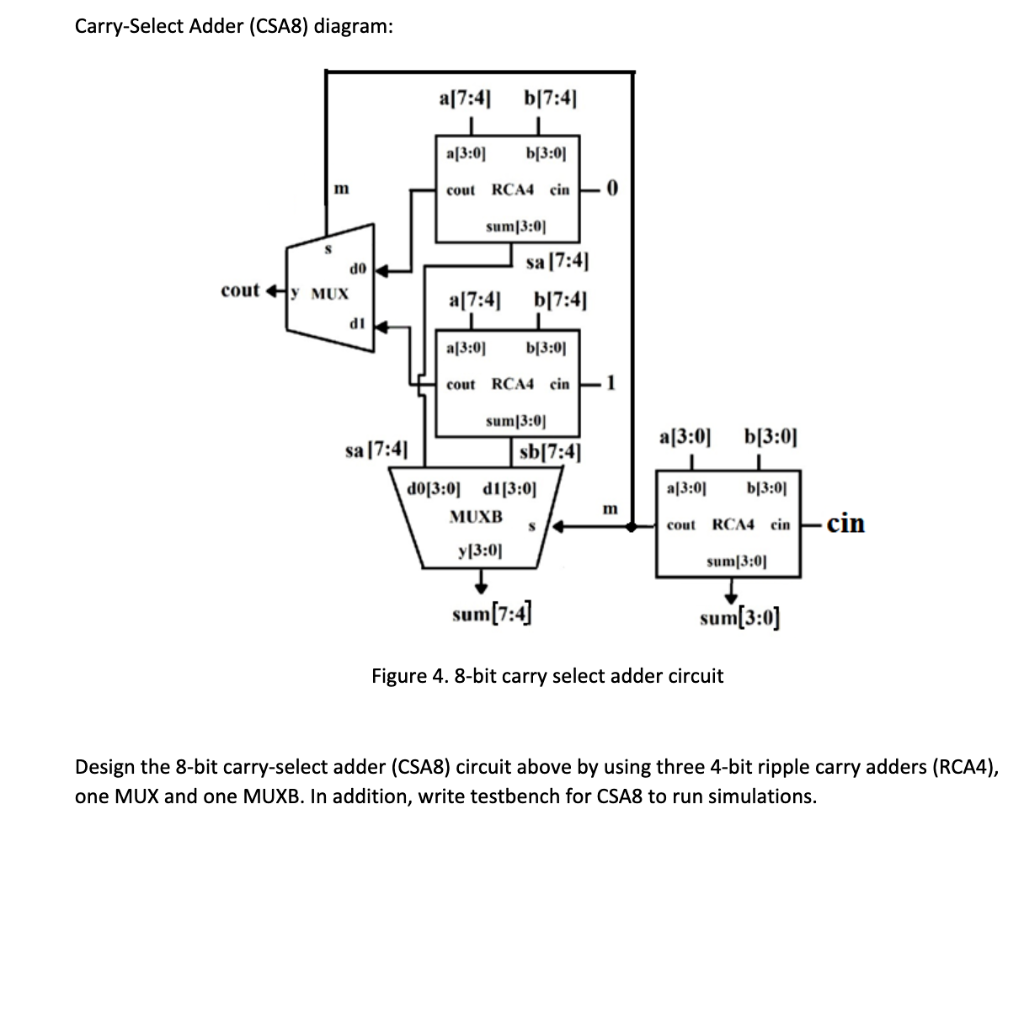

Carry-Select Adder (CSA8) diagram: a[7:41 b17:4) a(3:0) b[3:00 cout RCA4 cin0 sum[3:01 sa 17:41 dok cout y MUX a17:41 b17:4) di a[3:0) b[3:01 cout RCA4 cin1 b[3:0) sum|3:0) sa 17:41 sb[7:4) d0[3:0) d1[3:0) MUXB a(3:0) 1 a[3:01 b[3:01 m s cout RCA4 cin -cin y[3:0) sum[3:0) sum[7:4] sum[3:0) Figure 4. 8-bit carry select adder circuit Design the 8-bit carry-select adder (CSA8) circuit above by using three 4-bit ripple carry adders (RCA4), one MUX and one MUXB. In addition, write testbench for CSA8 to run simulations. Carry-Select Adder (CSA8) diagram: a[7:41 b17:4) a(3:0) b[3:00 cout RCA4 cin0 sum[3:01 sa 17:41 dok cout y MUX a17:41 b17:4) di a[3:0) b[3:01 cout RCA4 cin1 b[3:0) sum|3:0) sa 17:41 sb[7:4) d0[3:0) d1[3:0) MUXB a(3:0) 1 a[3:01 b[3:01 m s cout RCA4 cin -cin y[3:0) sum[3:0) sum[7:4] sum[3:0) Figure 4. 8-bit carry select adder circuit Design the 8-bit carry-select adder (CSA8) circuit above by using three 4-bit ripple carry adders (RCA4), one MUX and one MUXB. In addition, write testbench for CSA8 to run simulations

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts