Question: Please show all work and steps and explanations. The scribbled part says 11100xxxxxxxxxxx Consider the following memory read timing specification for a synchronous bus, where

Please show all work and steps and explanations.

The scribbled part says 11100xxxxxxxxxxx

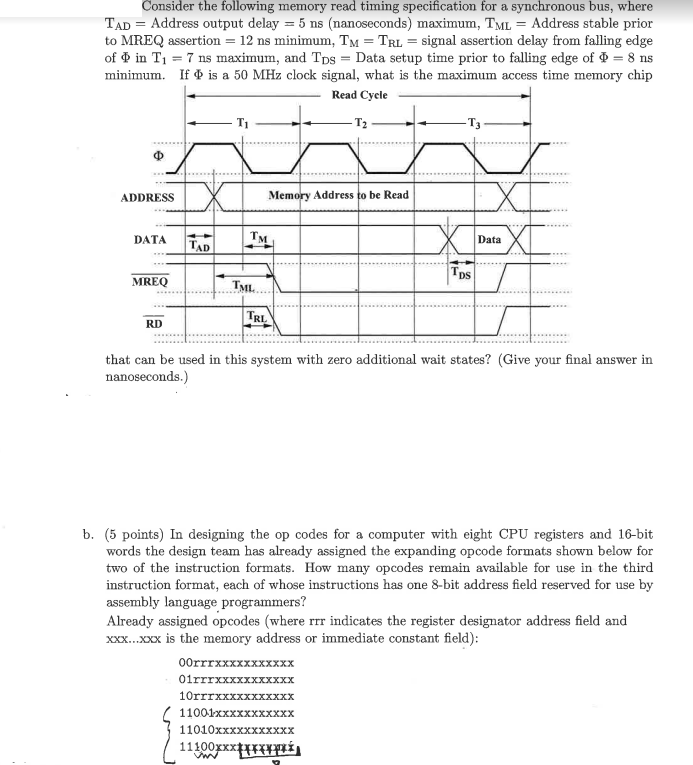

Consider the following memory read timing specification for a synchronous bus, where TAD = Address output delay 5 ns (nanoseconds) maximum. TML = Address stable prior to MREQ assertion = 12 ns minimum. TM = TRL-signal assertion delay from falling edge of in T-7 ns maximum, and TDS Data setup time prior to falling edge of -8 ns minimum. If is a 50 MHz clock signal, what is the maximum access time memory chip Read Cycle T3 ADDRESS Men Address to be Read DATA Data AD | DS MREQ RL RD that can be used in this system with zero additional wait states? (Give your final answer in nanoseconds.) b. (5 points) In designing the op codes for a computer with eight CPU registers and 16-bit words the design team has already assigned the expanding opcode formats shown below for two of the instruction formats. How many opcodes remain available for use in the third instruction format, each of whose instructions has one 8-bit address field reserved for use by assembly language programmers? Already assigned opcodes (where rrr indicates the register designator address field and xxx...xxx is the memory address or immediate constant field) 11001xxxxxxxxxxx 11010xxxxxxxxxxx 11100 Consider the following memory read timing specification for a synchronous bus, where TAD = Address output delay 5 ns (nanoseconds) maximum. TML = Address stable prior to MREQ assertion = 12 ns minimum. TM = TRL-signal assertion delay from falling edge of in T-7 ns maximum, and TDS Data setup time prior to falling edge of -8 ns minimum. If is a 50 MHz clock signal, what is the maximum access time memory chip Read Cycle T3 ADDRESS Men Address to be Read DATA Data AD | DS MREQ RL RD that can be used in this system with zero additional wait states? (Give your final answer in nanoseconds.) b. (5 points) In designing the op codes for a computer with eight CPU registers and 16-bit words the design team has already assigned the expanding opcode formats shown below for two of the instruction formats. How many opcodes remain available for use in the third instruction format, each of whose instructions has one 8-bit address field reserved for use by assembly language programmers? Already assigned opcodes (where rrr indicates the register designator address field and xxx...xxx is the memory address or immediate constant field) 11001xxxxxxxxxxx 11010xxxxxxxxxxx 11100

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts