Question: Please solve all questions 2. If a processor's TLB has a hit rate of 80 percent, and it takes 150 cycles to search the page

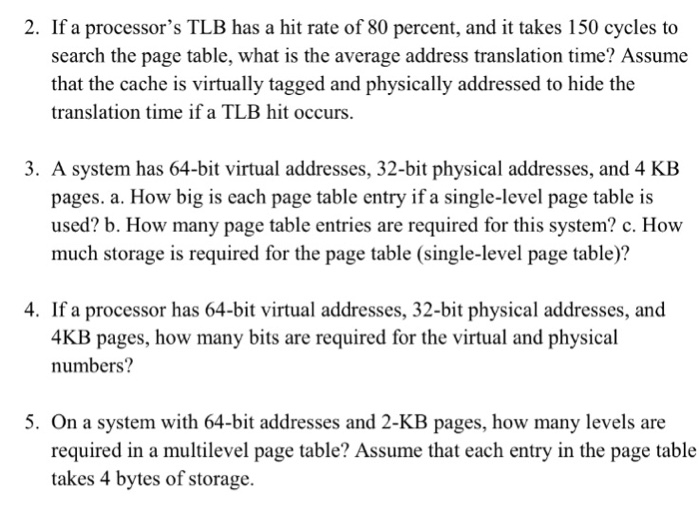

2. If a processor's TLB has a hit rate of 80 percent, and it takes 150 cycles to search the page table, what is the average address translation time? Assume that the cache is virtually tagged and physically addressed to hide the translation time if a TLB hit occurs. 3. A system has 64-bit virtual addresses, 32-bit physical addresses, and 4 KB pages. a. How big is each page table entry if a single-level page table is used? b. How many page table entries are required for this system? c. How much storage is required for the page table (single-level page table)? 4. If a processor has 64-bit virtual addresses, 32-bit physical addresses, and 4KB pages, how many bits are required for the virtual and physical numbers? 5. On a system with 64-bit addresses and 2-KB pages, how many levels are required in a multilevel page table? Assume that each entry in the page table takes 4 bytes of storage

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts