Question: Please solve all the question 2. For a cache with 128-byte cache line, give the address of the first word and last word in the

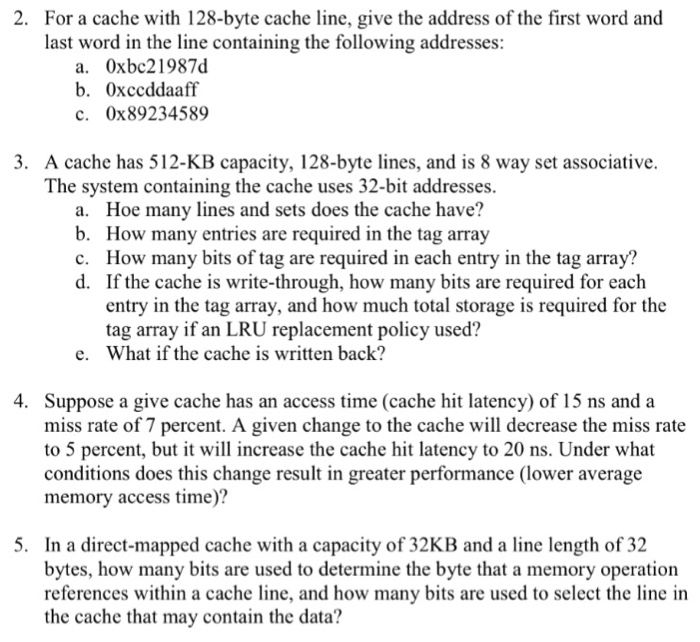

2. For a cache with 128-byte cache line, give the address of the first word and last word in the line containing the following addresses: a. 0xbc21987d b. Oxccddaaff c. 0x89234589 3. A cache has 512-KB capacity, 128-byte lines, and is 8 way set associative. The system containing the cache uses 32-bit addresses a. Hoe many lines and sets does the cache have? b. How many entries are required in the tag array c. How many bits of tag are required in each entry in the tag array? d. If the cache is write-through, how many bits are required for each entry in the tag array, and how much total storage is required for the tag array if an LRU replacement policy used? What if the cache is written back? e. 4. Suppose a give cache has an access time (cache hit latency) of 15 ns and a miss rate of 7 percent. A given change to the cache will decrease the miss rate to 5 percent, but it will increase the cache hit latency to 20 ns. Under what conditions does this change result in greater performance (lower average memory access time)? 5. In a direct-mapped cache with a capacity of 32KB and a line length of 32 bytes, how many bits are used to determine the byte that a memory operation references within a cache line, and how many bits are used to select the line in the cache that may contain the data

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts