Question: Please solve d, e, f What is the minimum number of flip flops needed to implement this circuit as it is currently described by the

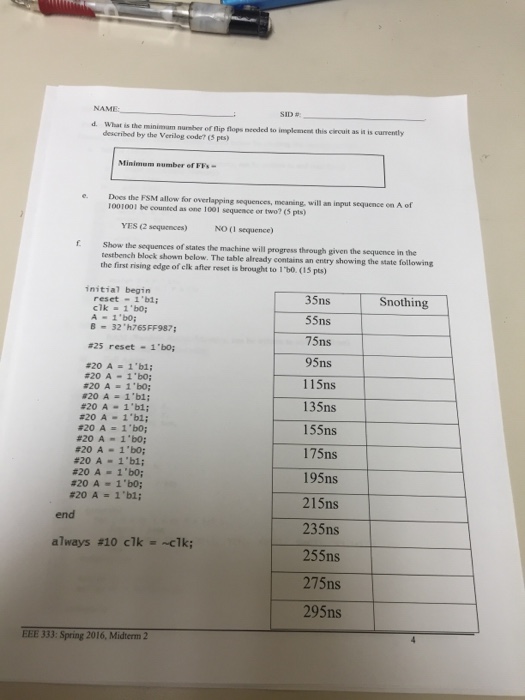

What is the minimum number of flip flops needed to implement this circuit as it is currently described by the Verilog code? Does the FSM allow for overlapping sequences, meaning, will an input sequence on A of 1001001 be counted as one 1001 sequence or two? YES(2 sequences) NO(1 sequence) Show the sequence of states the machine will program through given the sequence in the test bench block shown below. The table already contains an entry showing the state following the first rising edge of clk after reset is brought to 1 'b0. Initial begin reset = 1 'b1; clk = 1 'b0; A = 1 'b0; B = 32'h765FF987; #25 reset = 1 'b0; #20 A = 1 'b1; #20 A = 1 'b0; #20 A = 1 'b0; #20 A = 1 'b1; #20 A = 1 'b1; #20 A = 1 'b1; #20 A = 1 'b0; #20 A = 1 'b0; #20 A = 1 'b0; #20 A = 1 'b1; #20 A = 1 'b0; #20 A = 1 'b0; #20 A = 1 'b1; end always #10 clk = ~clk; What is the minimum number of flip flops needed to implement this circuit as it is currently described by the Verilog code? Does the FSM allow for overlapping sequences, meaning, will an input sequence on A of 1001001 be counted as one 1001 sequence or two? YES(2 sequences) NO(1 sequence) Show the sequence of states the machine will program through given the sequence in the test bench block shown below. The table already contains an entry showing the state following the first rising edge of clk after reset is brought to 1 'b0. Initial begin reset = 1 'b1; clk = 1 'b0; A = 1 'b0; B = 32'h765FF987; #25 reset = 1 'b0; #20 A = 1 'b1; #20 A = 1 'b0; #20 A = 1 'b0; #20 A = 1 'b1; #20 A = 1 'b1; #20 A = 1 'b1; #20 A = 1 'b0; #20 A = 1 'b0; #20 A = 1 'b0; #20 A = 1 'b1; #20 A = 1 'b0; #20 A = 1 'b0; #20 A = 1 'b1; end always #10 clk = ~clk

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts