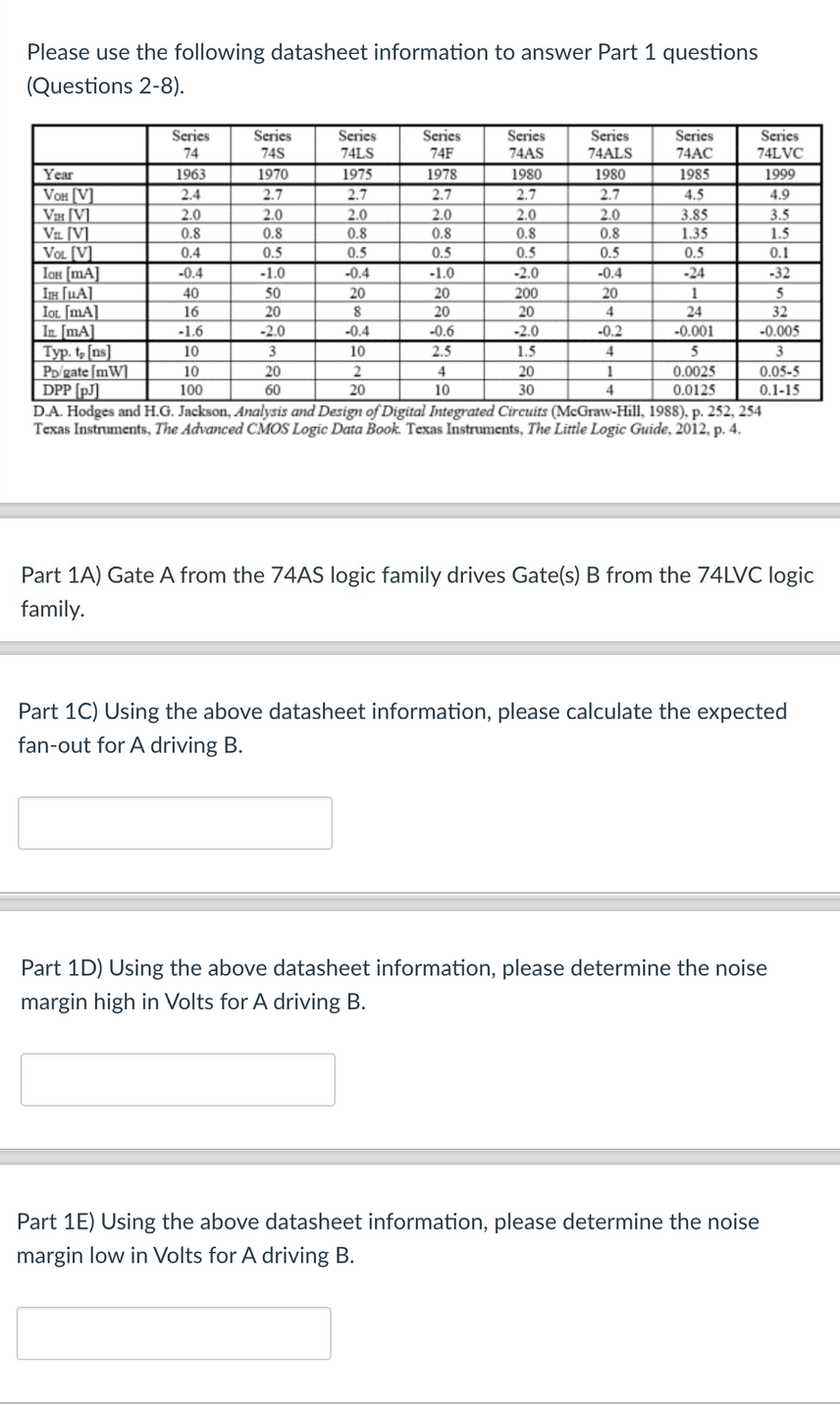

Question: Please use the following datasheet information to answer Part 1 questions (Questions 2-8). 1975 Series Series Series Series Series Series Series Series 74 745 74LS

Please use the following datasheet information to answer Part 1 questions (Questions 2-8). 1975 Series Series Series Series Series Series Series Series 74 745 74LS 74F 74AS 74ALS 74AC 74LVC Year 1963 1970 1978 1980 1980 1985 1999 VOHV 2.4 2.7 2.7 2.7 2.7 2.7 4.5 4.9 VHV 2.0 2.0 2.0 2.0 2.0 2.0 3.85 3.5 V.LV 0.8 0.8 0.8 0.8 0.8 0.8 1.35 1.5 VOLV 0.4 0.5 0.5 0.5 0.5 0.5 0.5 0.1 low (mA) -0.4 -1.0 -0.4 -1.0 -2.0 -0.4 -24 -32 IH (UA) 40 50 20 20 200 20 1 5 IormA] 16 20 8 20 20 4 24 32 In [mA -1.6 -2.0 -0.4 -0.6 -0.2 -0.001 -0.005 Typ. t, [ns] 10 3 10 2.5 1.5 4 5 3 Pp/gate [mW] 10 20 2 4 20 1 0.0025 0.05-5 DPP (PJ) 100 60 20 10 30 4 0.0125 0.1-15 D.A. Hodges and H.G. Jackson, Analysis and Design of Digital Integrated Circuits (McGraw-Hill, 1988), p. 252, 254 Texas Instruments, The Advanced CMOS Logic Data Book. Texas Instruments, The Little Logic Guide, 2012, p. 4. -2.0 Part 1A) Gate A from the 74AS logic family drives Gate(s) B from the 74LVC logic family. Part 1C) Using the above datasheet information, please calculate the expected fan-out for A driving B. Part 1D) Using the above datasheet information, please determine the noise margin high in Volts for A driving B. Part 1E) Using the above datasheet information, please determine the noise margin low in Volts for A driving B. Please use the following datasheet information to answer Part 1 questions (Questions 2-8). 1975 Series Series Series Series Series Series Series Series 74 745 74LS 74F 74AS 74ALS 74AC 74LVC Year 1963 1970 1978 1980 1980 1985 1999 VOHV 2.4 2.7 2.7 2.7 2.7 2.7 4.5 4.9 VHV 2.0 2.0 2.0 2.0 2.0 2.0 3.85 3.5 V.LV 0.8 0.8 0.8 0.8 0.8 0.8 1.35 1.5 VOLV 0.4 0.5 0.5 0.5 0.5 0.5 0.5 0.1 low (mA) -0.4 -1.0 -0.4 -1.0 -2.0 -0.4 -24 -32 IH (UA) 40 50 20 20 200 20 1 5 IormA] 16 20 8 20 20 4 24 32 In [mA -1.6 -2.0 -0.4 -0.6 -0.2 -0.001 -0.005 Typ. t, [ns] 10 3 10 2.5 1.5 4 5 3 Pp/gate [mW] 10 20 2 4 20 1 0.0025 0.05-5 DPP (PJ) 100 60 20 10 30 4 0.0125 0.1-15 D.A. Hodges and H.G. Jackson, Analysis and Design of Digital Integrated Circuits (McGraw-Hill, 1988), p. 252, 254 Texas Instruments, The Advanced CMOS Logic Data Book. Texas Instruments, The Little Logic Guide, 2012, p. 4. -2.0 Part 1A) Gate A from the 74AS logic family drives Gate(s) B from the 74LVC logic family. Part 1C) Using the above datasheet information, please calculate the expected fan-out for A driving B. Part 1D) Using the above datasheet information, please determine the noise margin high in Volts for A driving B. Part 1E) Using the above datasheet information, please determine the noise margin low in Volts for A driving B

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts