Question: Please write vhdl for problem 1 MEW Be careful-files from the Internet can contain viruses. Unless you need to edit, it's safer to stay in

Please write vhdl for problem 1

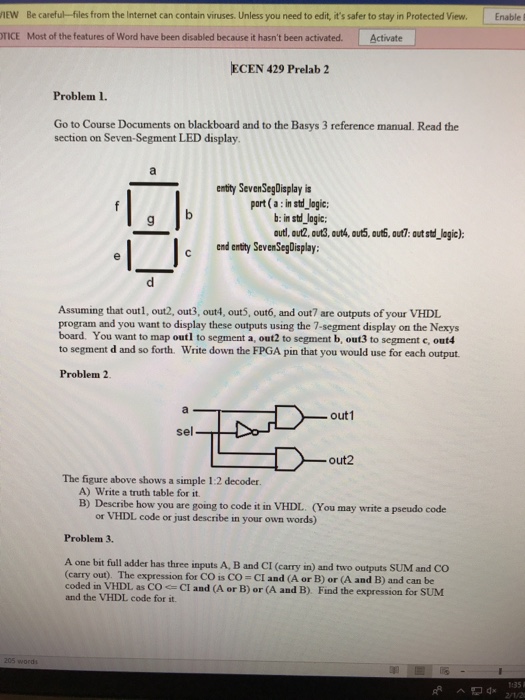

Please write vhdl for problem 1 MEW Be careful-files from the Internet can contain viruses. Unless you need to edit, it's safer to stay in Protected View. Enable I TICE Most of the features of Word have been disabled because it hasn't been activated. Activate ECEN 429 Prelab 2 Problem 1. Go to Course Documents on blackboard and to the Basys 3 reference manual. Read the section on Seven-Segment LED display entity SevenSegDisplay is ort (a : in std Jogic b: in std logic outl, out2,outh, out5, outG. ou 7: out std_logic); c end entity evenSegDisplay Assuming that out1, out2, out3, out4, out5, out6, and out7 are outputs of your VHDL program and you want to display these outputs using the 7-segment display on the Nexys board. You want to map outl to segment a, out2 to segment b, out3 to segment c, out4 to segment d and so forth. Write down the FPGA pin that you would use for each output. Problem 2 out1 sel out2 The figure above shows a simple 1:2 decoder A) Write a truth table for it B) Describe how you are going to code it in VHDL. (You may write a pseudo code or VHDL code or just describe in your own words) Problem 3. A one bit full adder has three inputs A, B and CI (carry in) and two outputs SUM and CO (carry out). The expression for CO is CO - CI and (A or B) or (A and B) and can be coded in VHDL as CO CI and (A or B) or (A and B) Find the expression for SUM and the VHDL code for it 1:35 MEW Be careful-files from the Internet can contain viruses. Unless you need to edit, it's safer to stay in Protected View. Enable I TICE Most of the features of Word have been disabled because it hasn't been activated. Activate ECEN 429 Prelab 2 Problem 1. Go to Course Documents on blackboard and to the Basys 3 reference manual. Read the section on Seven-Segment LED display entity SevenSegDisplay is ort (a : in std Jogic b: in std logic outl, out2,outh, out5, outG. ou 7: out std_logic); c end entity evenSegDisplay Assuming that out1, out2, out3, out4, out5, out6, and out7 are outputs of your VHDL program and you want to display these outputs using the 7-segment display on the Nexys board. You want to map outl to segment a, out2 to segment b, out3 to segment c, out4 to segment d and so forth. Write down the FPGA pin that you would use for each output. Problem 2 out1 sel out2 The figure above shows a simple 1:2 decoder A) Write a truth table for it B) Describe how you are going to code it in VHDL. (You may write a pseudo code or VHDL code or just describe in your own words) Problem 3. A one bit full adder has three inputs A, B and CI (carry in) and two outputs SUM and CO (carry out). The expression for CO is CO - CI and (A or B) or (A and B) and can be coded in VHDL as CO CI and (A or B) or (A and B) Find the expression for SUM and the VHDL code for it 1:35

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts